Синтез ЛПВП жалуется на отсутствие сигналов в списке чувствительности

Здравствуйте, у меня есть этот простой процесс VHDL (генерируется из кода MyHDL):

DIGIPOT_CONTROLLER_CONNECTCLOCK: process (delayedClock) is

begin

if to_boolean(clkEn) then

if to_boolean(delayedClock) then

scl_d <= '0';

else

scl_d <= 'Z';

end if;

else

if to_boolean(sclIdleValue) then

scl_d <= 'Z';

else

scl_d <= '0';

end if;

end if;

end process DIGIPOT_CONTROLLER_CONNECTCLOCK;

Оригинальный код MyHDL:

@always(delayedClock)

def connectClock():

if(clkEn):

if(delayedClock):

scl_d.next = False

else:

scl_d.next = None

else:

if(sclIdleValue):

scl_d.next = None

else:

scl_d.next = False

В симуляции это работает отлично (и симулятор ISIM и MyHDL), но когда я пытаюсь синтезировать его в Spartan 6, он выдает следующие предупреждения: clken должен быть в списке чувствительности процесса, sclidlevalue должен быть в списке чувствительности процесса.

Что я понимаю, что это как-то выводило, что этот процесс должен быть чувствительным к сигналам clkEn и sclIdleValue. Но, конечно, это не то, что я хотел. Я хочу, чтобы он изменял вывод только тогда, когда delayedClock меняет свое состояние, а не когда clkEn или sclIdleValue изменяют свои соответствующие состояния.

Это что-то, чего нельзя было сделать в архитектуре Spartan 6? Или я должен описать процесс иначе, чтобы иметь намеченное поведение?

1 ответ

Я наконец-то понял, что в результате получается код MyHDL:

@always(delayedClock.posedge, reset.posedge)

def connectClock():

if(reset == 1):

delayedClock_int.next = True

else:

delayedClock_int.next = not delayedClock_int

if(clkEn):

if(delayedClock_int):

scl_d.next = False

else:

scl_d.next = None

else:

if(sclIdleValue):

scl_d.next = None

else:

scl_d.next = False

и (сгенерированный) VHDL:

DIGIPOT_CONTROLLER_CONNECTCLOCK: process (delayedClock, reset) is

begin

if (reset = '1') then

delayedClock_int <= '1';

elsif rising_edge(delayedClock) then

delayedClock_int <= to_std_logic((not to_boolean(delayedClock_int)));

if to_boolean(clkEn) then

if to_boolean(delayedClock_int) then

scl_d <= '0';

else

scl_d <= 'Z';

end if;

else

if to_boolean(sclIdleValue) then

scl_d <= 'Z';

else

scl_d <= '0';

end if;

end if;

end if;

end process DIGIPOT_CONTROLLER_CONNECTCLOCK;

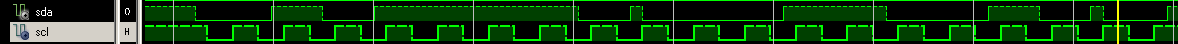

Мне пришлось увеличить задержку тактовых импульсов в два раза по частоте (а затем разделить их на два в моем процессе connectClock), таким образом, он дает тот же результат, что и исходный процесс, и его можно использовать без предупреждения. Причиной отказа от синхронизации является SCL I2C. Форма волны, как показано здесь: