Мультиплексор в vhdl со структурным дизайном

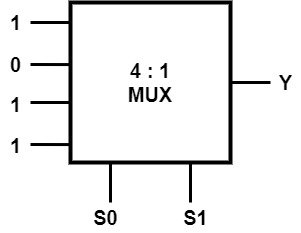

Я совершенно не знаком с VHDL и хочу реализовать следующий мультиплексор для логического вывода S0 => S1 без использования других вентилей.

Я хочу использовать структурный дизайн, но одна из моих основных проблем заключается в том, что я не понимаю, как правильно сопоставить порты, чтобы реализовать данный вывод.

Пока мой код компилируется, iSim запускается, но я получаю два предупреждения:

- mux41_impl остается черным ящиком, так как не имеет привязки.

- mux_out_test имеет значение U

Кроме того, я понимаю, что мой компонент должен точно соответствовать объекту, но если я переименую его в имя объекта, я получаю сообщение о недопустимом повторении.

код

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity MUX41_IMPL_top is

port (

D0, D1, D2, D3, S0, S1: in STD_LOGIC;

mux_out : out STD_LOGIC

);

end MUX41_IMPL_top;

architecture structure of MUX41_IMPL_top is

component MUX41_IMPL

port (

D0, D1, D2, D3, S0, S1: in STD_LOGIC;

mux_out : out STD_LOGIC

);

end component;

begin

u1: MUX41_IMPL port map (D0, D1, D2, D3, S0, S1, mux_out);

end structure;

код тестовой среды

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity MUX41_IMPL_SIMBOX is

end MUX41_IMPL_SIMBOX;

architecture TEST_MUX41_IMPL of MUX41_IMPL_SIMBOX is

component MUX41_IMPL is

port (

D0, D1, D2, D3, S0, S1: in STD_LOGIC;

mux_out : out STD_LOGIC

);

end component;

signal D0_test : STD_LOGIC := '1';

signal D1_test : STD_LOGIC := '0';

signal D2_test : STD_LOGIC := '1';

signal D3_test : STD_LOGIC := '1';

signal S0_test, S1_test : STD_LOGIC := '0';

signal mux_out_test : STD_LOGIC;

for my_MUX41_IMPL : MUX41_IMPL use entity work.MUX41_IMPL_top(structure);

begin

my_MUX41_IMPL : MUX41_IMPL

port map (

D0 => D0_test,

D1 => D1_test,

D2 => D2_test,

D3 => D3_test,

S0 => S0_test,

S1 => S1_test,

mux_out => mux_out_test

);

S0_test <= not S0_test after 2 ns;

S1_test <= not S1_test after 4 ns;

end TEST_MUX41_IMPL;

1 ответ

Решение

entity MUX41_IMPL_top is

port (

D0, D1, D2, D3: in STD_LOGIC;

Sel : in std_logic_vector(1 downto 0);

mux_out : out STD_LOGIC

);

end MUX41_IMPL_top;

architecture structure of MUX41_IMPL_top is

begin

with Sel select

mux_out <= D0 when "00",

D1 when "01",

D2 when "10",

D3 when "11",

'0' when others;

architecture structure;