VHDL - Почему мой регистровый выход изменяется, когда нет ни тактового фронта, ни сброса?

Я реализовал регистр в VHDL, используя следующий код:

library ieee;

use ieee.std_logic_1164.all;

entity reg is

generic (

width : integer := 8

);

port (

reset, clk, en : in std_logic;

d : in std_logic_vector(width - 1 downto 0);

q : out std_logic_vector(width - 1 downto 0)

);

end reg;

architecture Behavioral of reg is

begin

regProc : process (clk, reset, en, d)

begin

if reset = '1' then

q <= (others => '0');

elsif rising_edge(clk) and en = '1' then

q <= d;

end if;

end process;

end Behavioral;

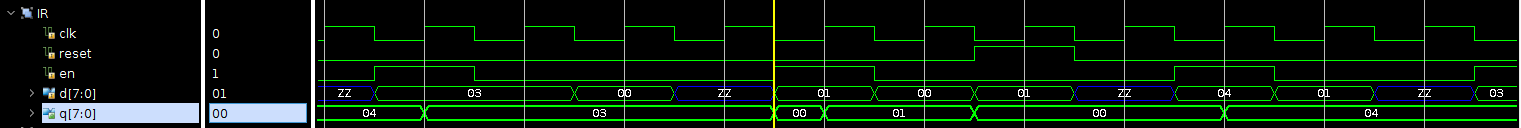

Я заметил при моделировании, что он иногда меняет свой выход, когда нет ни фронта тактового сигнала, ни сброса. Я включил формы волны из моделирования Вивадо ниже, где интересующее событие происходит у желтого маркера. Кто-нибудь может объяснить это поведение мне, пожалуйста? Благодарю.