LFSR не генерирует случайные значения во время моделирования

Я новичок в VHDL, но есть идея. Я сделал этот LFSR, но не знаю, почему он застрял между начальным значением seed и другим значением XOR. Я работаю с Altera Quartus 16 Lite и ISim.

library ieee;

use ieee.std_logic_1164.all;

--creating a galois LFSR

entity LFSR is

port (

clk : in std_logic;

rst : in std_logic;

en : in std_logic;

rdm_out : out std_logic_vector(15 downto 0);

rdm_out_a : out std_logic_vector(7 downto 0);

rdm_out_b : out std_logic_vector(7 downto 0);

lfsr_Done : out std_logic --lfsr done

);

end entity LFSR;

architecture behavioral of LFSR is

signal temp_out : std_logic_vector(15 downto 0) := (0 => '1' ,others => '0'); --initial value as seed

signal temp_done : std_logic;

begin

process (clk, rst)

begin

if rising_edge (clk) then --module operates only when enabled

if (rst = '1') then

temp_out <= (0 => '1' ,others => '0');

temp_done <= '0';

elsif (en = '1') then

temp_out <= temp_out(15 downto 11) & (temp_out(10) xor temp_out(0)) & temp_out(9 downto 5) & (temp_out(4) xor temp_out(0)) & temp_out(3 downto 0);

--temp_out <= (temp_out(15) xor temp_out(0)) & (temp_out(14) xor temp_out(0)) & temp_out(13) & (temp_out(12) xor temp_out(0)) & temp_out(11 downto 4) & (temp_out(3) xor temp_out(0)) & temp_out(2 downto 0);

temp_done <= '1';

end if;

end if;

end process;

rdm_out <= temp_out(15 downto 0);

rdm_out_a <= temp_out(15 downto 8);

rdm_out_b <= temp_out(7 downto 0);

lfsr_Done <= temp_done;

end architecture behavioral;`

Закомментированный temp_out фактическая обратная связь (количество нажатий - 16,15,13 и 4), как я проверил случайными нажатиями, но все еще без улучшения.

И тестовый стенд, который я использовал, это:

library ieee;

use ieee.std_logic_1164.all;

entity lfsr_tb is

end lfsr_tb;

architecture test_bench of lfsr_tb is

component LFSR

port (

clk : in std_logic;

rst : in std_logic;

en : in std_logic;

rdm_out : out std_logic_vector(15 downto 0);

rdm_out_a : out std_logic_vector(7 downto 0);

rdm_out_b : out std_logic_vector(7 downto 0);

lfsr_Done : out std_logic );

end component;

signal clk1: std_logic;

signal rst1: std_logic;

signal en1 : std_logic;

signal rdm_out1 : std_logic_vector(15 downto 0);

signal rdm_out_a1 : std_logic_vector(7 downto 0);

signal rdm_out_b1 : std_logic_vector(7 downto 0);

signal lfsr_Done1 : std_logic ;

begin

mapping: LFSR port map(

clk => clk1,

rst => rst1,

en => en1,

rdm_out => rdm_out1,

rdm_out_a => rdm_out_a1,

rdm_out_b => rdm_out_b1,

lfsr_Done => lfsr_Done1 );

clock: process

begin

clk1 <= '0'; wait for 10 ps;

clk1 <= '1'; wait for 10 ps;

end process;

reset: process

begin

rst1 <= '1'; wait for 10 ps;

rst1 <= '0';

en1 <= '1'; wait for 800 ps;

end process;

end test_bench;

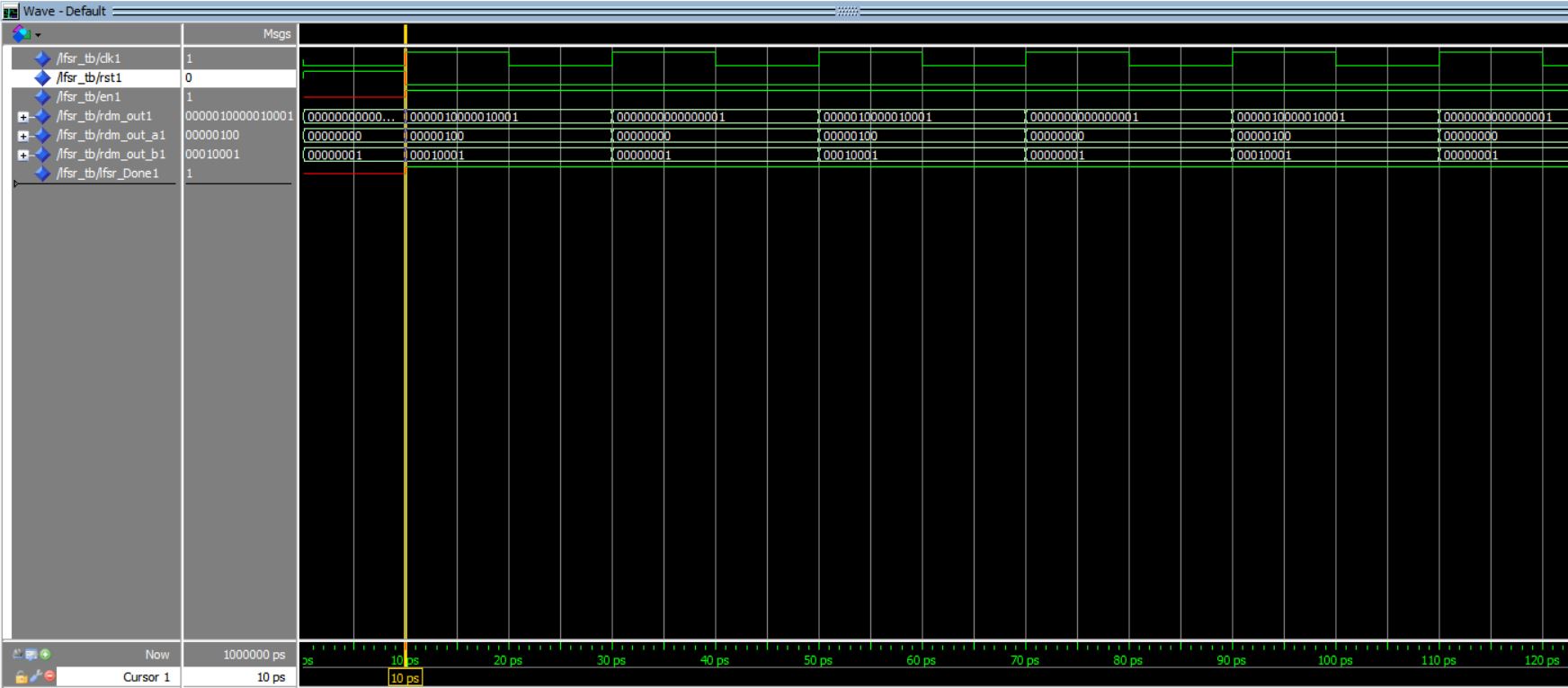

Вот результат, который я получаю:

1 ответ

Да, он не сдвигался, но сейчас он работает.

temp_out(15) <= temp_out(0);-- shifting bit

temp_out(14) <= temp_out(15);

temp_out(13) <= temp_out(14) xor temp_out(0);

temp_out(12) <= temp_out(13) xor temp_out(0);

temp_out(11) <= temp_out(12);

temp_out(10) <= temp_out(11) xor temp_out(0);

temp_out(9 downto 0) <= temp_out(10 downto 1);

Надеюсь, что это помогает другим. Спасибо, парни