Нарушение прав доступа при компиляции (шаг синтеза) в Quartus II с системой Qsys

В Quartus II (V15.02) во время компиляции (шаг "Анализ и синтез") я получаю следующую ошибку, когда назначаю карту портов для проекта qsys в моем верхнем объекте:

-------------------------------------------------- ------------

Ошибка детали ошибки:

Неустранимая ошибка: нарушение прав доступа в 0000000000000000 Модуль: quartus_map.exe Не удалось получить трассировку стека

Исполняемый файл: quartus_map

Комментарий:

Никто

Системная информация

Платформа: windows64

Название ОС: Windows 7 // Я использую Win 10 64bit

Версия ОС: 6.2

Информация о Quartus II

Адресные биты: 64

Версия: 15.0.2

Телосложение: 153

Издание: полная версия

-------------------------------------------------- ------------

После того, как я очистил проект (Project -> Revision name: * -> OK), я получаю упомянутую ошибку каждый раз, когда я запускаю Analysis & Synthesis.

Мой проект содержит: Файл VHDL. Импортированный файл.qip, созданный с помощью QSYS. В QSYS я сгенерировал новый файл hdl после первого появления ошибки, но.. тот же результат. Я тоже удалил порядок в БД, но результат все тот же. Проект работал

Мой проект содержал (до тех пор, пока впервые не появилась ошибка) сигнал Signal Tap и файл.sdc, а в файле sdc были следующие строки:

derive_clock_uncertainty

derive_pll_clocks

Я удалил файл.sdc со своего жесткого диска и попытался снова - тот же результат

Я удалил.qip файл, прокомментировал карту портов и скомпилировал - успех

Затем я сгенерировал новый файл HDL в QSYS.

После этого я добавил.qip файл в Quartus II (карта портов все еще комментируется) -> успех

Тогда я раскомментировал определения карты порта -> ошибка

Последние несколько журналов перед появлением сообщения об ошибке:

Информация (10264): Verilog HDL Информация о выписке из дела в altera_trace_transacto_lite.v(206): все выражения обуславливающих элементов в этом выписке являются одноразовыми

Информация (10264): Verilog HDL Информация о выписке из дела в altera_trace_transacto_lite.v(314): все выражения обуславливающих элементов в этом выписке являются одноразовыми

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(92): объекту "state_read_addr" присвоено значение, но оно никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(96): объекту "state_d1" присвоено значение, но он никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(98): объект "in_ready_d1" назначил значение, но никогда не читал

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(117): объекту "b_startofpacket_wire" присвоено значение, но он никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(123): объекту mem_readdata0 присвоено значение, но оно никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(128): объекту mem_readdata1 присвоено значение, но оно никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(133): объекту mem_readdata2 присвоено значение, но оно никогда не читается

Предупреждение (10858): предупреждение Verilog HDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(140): объект state_waitrequest используется, но никогда не назначается

Предупреждение (10036): Verilog HDL или VHDL предупреждение в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(141): объекту "state_waitrequest_d1" присвоено значение, но он никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(144): объекту "out_channel" присвоено значение, но оно никогда не читается. Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_ture_t_t_t_t_t_t_f_d_f_d_s_d_f_d_s_f_d_s_d_s_t_s_d_s_d_s_d_t_d_t_t_s__t_s___t_t_s_t_s_t_t_s_t_t_t_t_s_t_t_t_t_t_t_t_t_t_t_t_t_t_t_t_t_t_t_t_t_t_t_t:) присвоить значение, но никогда не читать

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(150): объекту "out_error" присвоено значение, но он никогда не читается

Предупреждение (10230): Предупреждение о назначении Verilog HDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(285): усеченное значение с размером 32, соответствующее размеру цели (1)

Предупреждение (10230): предупреждение о назначении Verilog HDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(301): усеченное значение с размером 32 для соответствия размеру цели (1)

Предупреждение (10230): Предупреждение о назначении Verilog HDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(317): усеченное значение с размером 32, соответствующее размеру цели (1)

Предупреждение (10230): предупреждение о назначении Verilog HDL в alt_sld_fab_alt_sld_fab_trfabric_capture_width.sv(334): усеченное значение с размером 32, соответствующее размеру цели (1)

Предупреждение (10036): Verilog HDL или VHDL предупреждение в alt_sld_fab_alt_sld_fab_trfabric_avalon_st_adapter_data_format_adapter_0.sv(92): объекту "state_read_addr" присвоено значение, но он никогда не читается

Предупреждение (10858): предупреждение Verilog HDL в alt_sld_fab_alt_sld_fab_trfabric_avalon_st_adapter_data_format_adapter_0.sv(137): объект state_waitrequest используется, но никогда не назначается

Предупреждение (10036): Verilog HDL или VHDL предупреждение в alt_sld_fab_alt_sld_fab_trfabric_avalon_st_adapter_data_format_adapter_0.sv(138): объекту "state_waitrequest_d1" присвоено значение, но он никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_avalon_st_adapter_data_format_adapter_0.sv(141): объекту "out_channel" присвоено значение, но он никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_trfabric_avalon_st_adapter_data_format_adapter_0.sv(147): объекту "out_error" присвоено значение, но он никогда не читается

Предупреждение (10230): предупреждение о назначении HDL Verilog в alt_sld_fab_alt_sld_fab_trfabric_avalon_st_adapter_data_format_adapter_0.sv(290): усеченное значение с размером 32 для соответствия размеру цели (2)

Предупреждение (10230): предупреждение о назначении HDL Verilog в alt_sld_fab_alt_sld_fab_trfabric_avalon_st_adapter_data_format_adapter_0.sv(311): усеченное значение с размером 32 для соответствия размеру цели (2)

Предупреждение (10230): предупреждение о назначении HDL Verilog в alt_sld_fab_alt_sld_fab_trfabric_avalon_st_adapter_data_format_adapter_0.sv(334): усеченное значение с размером 32 для соответствия размеру цели (2)

Предупреждение (10230): предупреждение о назначении HDL Verilog в alt_sld_fab_alt_sld_fab_trfabric_avalon_st_adapter_data_format_adapter_0.sv(353): усеченное значение с размером 32 для соответствия размеру цели (2)

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_host_link_jtag_h2t_timing.sv(82): объекту "in_ready" присвоено значение, но он никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_stfabric_mgmt_demux_port_adap.sv(74): объекту "out_channel" присвоено значение, но он никогда не читается

Предупреждение (10036): предупреждение Verilog HDL или VHDL в alt_sld_fab_alt_sld_fab_stfabric_mgmt_time_adap.sv(84): объекту "in_ready" присвоено значение, но он никогда не читается

Информация (12206): 2 дизайнерских перегородки требуют синтеза

Информация (12213): раздел "Top" требует синтеза, поскольку база данных проекта не содержит списка соединений после синтеза для этого раздела

Информация (12213): раздел "sld_hub:auto_hub" требует синтеза, поскольку база данных проекта не содержит списка соединений после синтеза для этого раздела

Информация (12209): ни один из разделов проекта не пропустит синтез в текущей инкрементной компиляции

С помощью этого кода я пытаюсь протестировать внешнюю тактовую частоту 50 МГц, которую я направляю в систему Qsys, и тактовую частоту 10 МГц от ФАПЧ, который я определил в Qsys, со светодиодным индикатором для каждого сигнала. Вот код от сущности верхнего уровня:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity helloworld_lab1 is

Port (

clk_50_max10 : in std_logic; --50MHz Clock

--clk_25_max10 : in std_logic; --25MHz Clock

--clk_10_adc : in std_logic; --10MHz Clock

cpu_resetn : in std_logic; -- Button 0

user_led : out std_logic_vector (4 downto 0);

user_pb : in std_logic_vector(3 downto 0); -- Middle Buttons

);

end entity helloworld_lab1;

architecture behaviour of helloworld_lab1 is

-- Qsys Component --

component helloworld_lab is

port (

clk_clk : in std_logic := 'X'; -- clk

reset_reset_n : in std_logic := 'X'; -- reset_n

pio_switch_external_connection_export : in std_logic_vector(1 downto 0) := (others => 'X'); -- export

pio_led_external_connection_export : out std_logic_vector(2 downto 0); -- export

pll_clock_clk : out std_logic -- export

);

end component helloworld_lab;

Signal cycle_counter : integer range 0 to 50000000; -- 50 MHz results in 1 Second

Signal pll_cycle_counter : integer range 0 to 10000000; -- 10 MHZ results in 1 Second

Signal led_1sec : std_logic:='0'; -- Signal LED 0

Signal led_pll : std_logic :='1'; -- Signal LED 4

Signal clock_pll : std_logic; -- Port Map PLL Clock

begin

blink_led_1s : process (clk_50_max10)

begin

if (rising_edge(clk_50_max10)) then

cycle_counter <= cycle_counter+1;

if (cycle_counter>=49999999) then

cycle_counter<=0;

led_1sec<=not led_1sec;

end if;

end if;

end process blink_led_1s;

user_led(0)<=led_1sec;

-----------------------------------------------------------------------

blink_led_pll : process (clock_pll)

begin

if (rising_edge(clock_pll))then

pll_cycle_counter <= pll_cycle_counter+1;

if (pll_cycle_counter<=9999999) then

pll_cycle_counter<=0;

led_pll<=not led_pll;

end if;

end if;

end process blink_led_pll;

user_led(4) <=led_pll;

---------------------------------------------------------------------

-----------------------------------Qsys port map-----------------------------------------------

QSYS : component helloworld_lab

port map (

clk_clk => clk_50_max10,

reset_reset_n => cpu_resetn,

pio_switch_external_connection_export => user_pb(3 downto 2),

pio_led_external_connection_export => user_led(3 downto 1),

pll_clock_clk => clock_pll

);

end architecture behaviour;

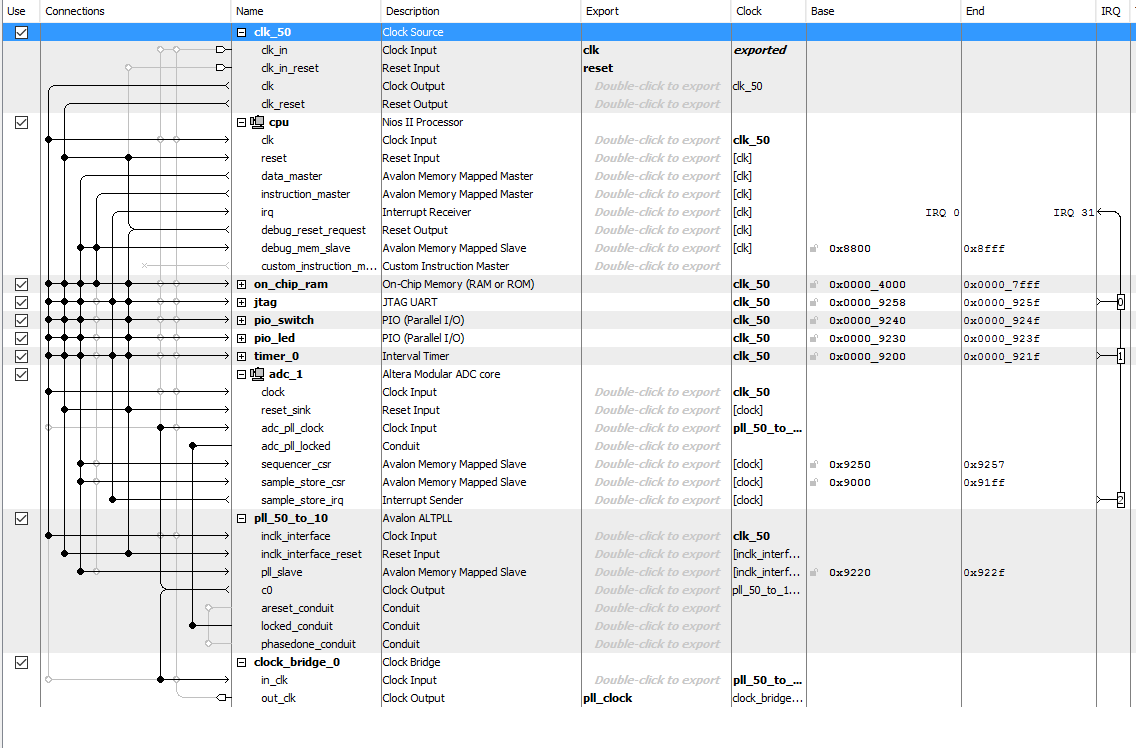

А вот скриншот системы Qsys.

Буду признателен за любую помощь в решении этой проблемы.