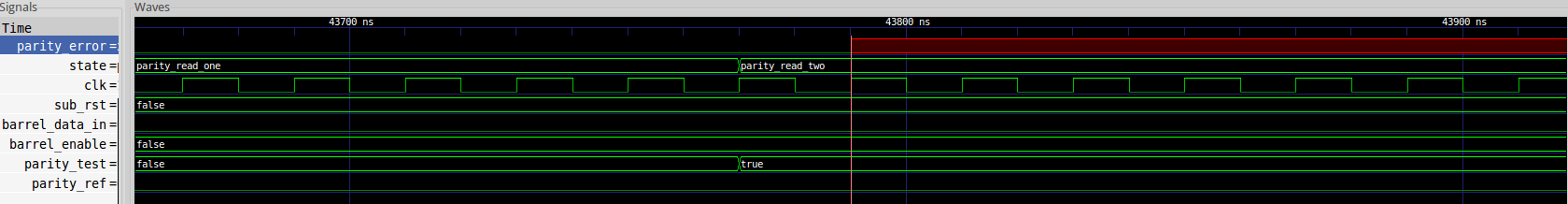

Сигнал падает до неопределенного, в то время как все связанные сигналы определены

Я пишу процесс, который должен искать каждый входящий бит, отслеживать погоду или нет, общее количество полученных единиц равно 1, и, когда придет время, нужно сравнить значение с эталонным значением. Процесс следующий:

parity_tester : process(clk, sub_rst, barrel_data_in, barrel_enable, parity_test, parity_ref)

variable last_known_enable : boolean := false;

variable last_known_data : STD_LOGIC := '0';

variable parity_error_out : STD_LOGIC := '0';

variable parity_ref_reg : STD_LOGIC := '0';

variable even : STD_LOGIC := '1';

begin

if sub_rst then

last_known_enable := false;

last_known_data := '0';

parity_error_out := '0';

even := '1';

elsif rising_edge(clk) then

if barrel_enable then

last_known_enable := true;

last_known_data := barrel_data_in;

else

if last_known_enable then

last_known_enable := false;

if last_known_data = '1' then

even := not even;

end if;

end if;

end if;

if parity_test then

case parity_bit_in_type is

when 0 =>

parity_error_out := even xnor parity_ref;

when 1 =>

parity_error_out := even xor parity_ref;

when 2 =>

parity_error_out := parity_ref;

when 3 =>

parity_error_out := not parity_ref;

when others =>

parity_error_out := '1';

end case;

end if;

end if;

parity_error <= parity_error_out;

end process;

Здесь я сталкиваюсь с проблемой: все сигналы, как определено в списке чувствительности процесса, определены, но согласно GHDL (симулятору) значение меняется на неопределенное всякий раз, когда parity_test переходит в true:  Что я делаю неправильно?

Что я делаю неправильно?

Я удалил то, что было здесь, потому что, когда я перешел на свой ноутбук, ошибка изменилась: речь идет о переключателе корпуса. Я до сих пор не понимаю, почему. parity_bit_in_type - это универсальный Natural с диапазоном (от 0 до 3). Если я возьму нужное мне утверждение (0 в этом случае) и удалим случай, то все будет работать, как положено. WebPack ISE, похоже, не жалуется на это, поэтому он начинает ощущаться как ошибка в GHDL.

GHDL версии:

/Downloads/ghdl-gcc-git » ghdl --version

GHDL 0.34dev (20151126) [Dunoon edition]

Compiled with GNAT Version: 5.3.0

mcode code generator

Written by Tristan Gingold.

Copyright (C) 2003 - 2015 Tristan Gingold.

GHDL is free software, covered by the GNU General Public License. There is NO

warranty; not even for MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.

Минимальный пример, который показывает то же поведение

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity uart_receiv_parity is

generic (

parity_bit_in_type : Natural range 0 to 3

);

port (

rst : in boolean;

clk : in STD_LOGIC;

parity_error : out STD_LOGIC -- Signals that the parity check has failed, is zero if there was none

);

end entity;

architecture Behavioral of uart_receiv_parity is

begin

parity_tester : process(clk, rst)

variable parity_error_out : STD_LOGIC := '0';

begin

if rst then

parity_error_out := '0';

elsif rising_edge(clk) then

case parity_bit_in_type is

when 0 =>

parity_error_out := '1';

when 1 =>

parity_error_out := '0';

when 2 =>

parity_error_out := '1';

when 3 =>

parity_error_out := '0';

when others =>

parity_error_out := '1';

end case;

end if;

parity_error <= parity_error_out;

end process;

end Behavioral;

1 ответ

В конце концов, это была моя ошибка: в тестовом стенде сигнал подавался из двух источников. Следовательно, "1" приводит к тому, что сигнал управляется как "1", так и "0", что приводит к "х". Когда сигнал должен был быть "0", выход был фактически нулевым.