Почему автобус Axi lite занимает два BRAM_18K?

Ниже приведен мой простой код:

void MyFunc(float input[10], float output[10])

{

#pragma HLS INTERFACE s_axilite port=input bundle=BUS_INPUT

const float temp[10]={

0.0f,0.1f,0.2f,0.3f,0.4f,0.5f,0.6f,0.7f,0.8f,0.9f

};

for(int i=0;i<10;i++)

{

output[i]=input[i]+temp[i];

}

}

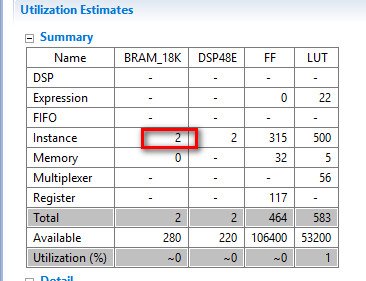

После обобщения использование ресурсов показано ниже,

Результат синтеза:

На этом рисунке я с удивлением обнаружил, что используются два блока BRAM_18K. Это нормально? а почему шина Axi lite может заткнуть два BRAM_18K?

Я проверил сгенерированный код verilog и до сих пор не смог найти причину. Сгенерированный код verilog помещается в https://drive.google.com/file/d/1iP6JQGbv6pShGuCF62G21isRHkjJhn3I/view?usp=sharing

Благодарю.

1 ответ

Ваше оборудование будет обрабатывать один блок данных, создавая второй блок данных. Оба блока должны быть где-то сохранены, и это хранилище является единицами оперативной памяти блока, как предполагает компилятор.