Процесс конвейерной обработки в VHDL?

В течение последних нескольких дней я искал метод написания небольшого числа VHDL для проекта, который позволил бы мне запускать обработку набора данных и передавать результаты. Устройство, которое я использую, может начать собирать второй набор данных, одновременно предоставляя полный первый набор для передачи моей ПЛИС, и я хочу воспользоваться этим с помощью конвейерной передачи, но я не добился успеха.

Для запуска сбора мне нужно отправить определенный набор сигналов в определенном порядке. После нескольких тактов и сигнала от ПЛИС весь набор выводится на несколько портов устройства. Моя цель состоит в том, чтобы весь процесс был запущен простым входным импульсом, и чтобы был возможен второй импульс во время выполнения назначений из первого импульса. Есть ли способ для меня отправить первый набор сигналов, а затем сигнал для вывода данных при одновременной отправке первого набора сигналов для второго сбора, если это имеет смысл?

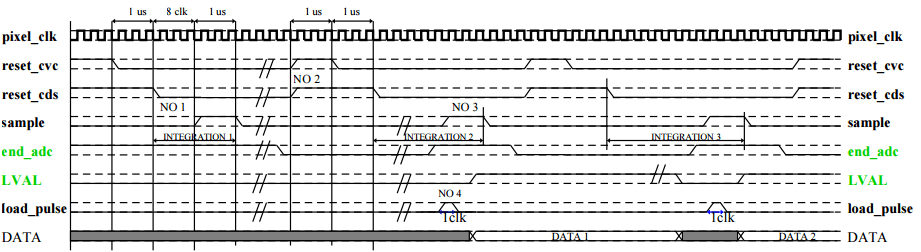

Вот картина того, что я имею в виду.

Как видите, данные из интеграции 1 отправляются во время второго и даже третьего этапа интеграции. load_pulse - это сигнал, который запрашивает вывод данных на DATAи это может произойти намного позже, когда отправляется второй набор сигналов для интегрирования 2.

Вот небольшой тестовый VHDL, который я написал, чтобы увидеть, возможно ли это с помощью простого процесса:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity test is

port(

x : in STD_LOGIC;

y : out STD_LOGIC := '0';

z : out STD_LOGIC := '0'

);

end test;

architecture test_behav of test is

begin

process(x) is

begin

y <= '0', '1' after 10 NS, '0' after 20 ns;

z <= '0', '1' after 30 NS, '0' after 40 ns;

end process;

end test_behav;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity testbench is

end testbench;

architecture testbench_behav of testbench is

component test is

port(

x : in STD_LOGIC;

y : out STD_LOGIC;

z : out STD_LOGIC

);

end component test;

signal x : STD_LOGIC := '0';

signal y : STD_LOGIC := '0';

signal z : STD_LOGIC := '0';

begin

testo: component test

port map(

x => x,

y => y,

z => z

);

x <= '1' after 25 ns;

end testbench_behav;

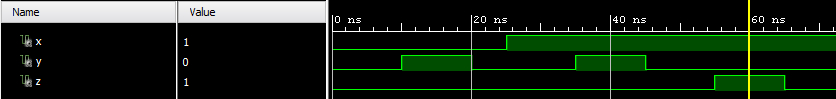

В этом примере я запускаю процесс, пока его назначения сигналов еще выполняются. Результатом здесь было то, что исходные назначения сигналов были прерваны, а новые назначения сигналов завершены после x <= '1' after 25 ns, как вы можете видеть здесь:

Есть ли способ сделать это, что вы можете объяснить мне или указать мне объяснение, или мне нужно будет использовать другой подход?

Спасибо