Xilinx, Zynq, AXI4 взаимосвязаны. Каковы последствия для производительности при настройке среза регистра и параметров данных fifo?

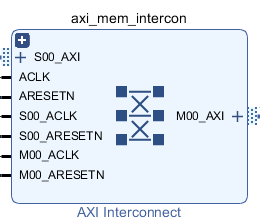

Рассмотрим межсоединение AXI4 на стороне PL (FPGA).

Когда я дважды щелкаю, чтобы увидеть доступные опции, в подчиненных интерфейсах появляется вкладка. Содержит следующие опции.

Какова цель включения среза регистра? Внешний относится к кэшу L2? А что означает Авто?

Какова цель включения Data FIFO? Для пакетных транзакций? Разве контроллер DMA не имеет своего собственного FIFO?

1 ответ

Зарегистрировать ломтики

Включение регистровых срезов ( AXI Interconnect v2.1 - стр. 93) в основном создает конвейер между вашим ведущим и подчиненным соединениями AXI, чтобы разорвать критический путь синхронизации. Кажется, он не имеет ничего общего с кэшем L2. Доступные опции предоставляют вам следующее (стр. 113):

- Если выбрано None (0), срез регистра не вставляется.

- Если выбрано Outer (1), срез SI вставляется на стороне SI иерархии ячеек SI-ответвителя.

- Если выбран Auto (2), срез регистра автоматически вставляется в иерархию ячеек SI-ответвителя, если обнаруживаются ячейки SI-ответвителя с общими путями синхронизации.

- Если выбрано Outer и Auto (3), срез SI вставляется на стороне SI иерархии ячеек SI-ответвителя, и может быть вставлен дополнительный срез регистра, если обнаруживаются ячейки SI-ответвителя с общими путями синхронизации.

Справочное руководство по AXI содержит руководство по оптимизации системы AXI на стр. 91. Например, в нем говорится: "Большие и сложные IP-блоки, такие как процессоры, контроллеры памяти DDR3 и мосты PCIe, являются хорошими кандидатами для включения секций регистров. Секция регистров нарушает временные тракты и предоставляет инструментам Place and Route (PAR) большую свободу для перемещения большого IP-блока в сторону от перегрузки ядра межсоединения и другой логики IP ". Тем не менее, я рекомендую прочитать весь этот раздел, поскольку чрезмерное использование разделов регистра может быть контрпродуктивным." И это действительно зависит от вашей системы.

Данные ФИФО

Цель включения Data FIFO - обеспечить буферизацию данных и повысить пропускную способность. Опция 32 глубокого режима обеспечивает FIFO на основе LUT-RAM глубиной 32 (только для канала данных), в то время как глубокий 512 (в пакетном режиме) обеспечивает пакетный FIFO на основе глубины 512 ГБ. Режим пакетного FIFO обеспечивает дополнительный 32-канальный FIFO в канале адреса с соответствующей расшифровкой, чтобы избежать полной / пустой задержки в середине пакетов. Это в основном добавляет задержку к операциям чтения / записи, чтобы избежать остановок. Прочитайте следующие страницы для получения более подробной информации. ( AXI Interconnect v2.1 - стр. 94). Опции предоставляют следующее:

- Если значение параметра равно 0, данные FIFO не вставляются.

- Если значение параметра равно 1, вставляется 32-канальный FIFO данных.

- Если значение параметра равно 2, вставляется FIFO данных глубиной 512 и активируется функция пакетного режима.

Наконец, я не знаю подробностей реализации DMA Xilinx, но я полагаю, что цель включения буфера была бы, если бы ваш принимающий модуль был не так быстр, как ваш DMA. Таким образом, DMA может предоставить больше данных, чем может прочитать ваш модуль, таким образом, буферизация его выходных данных может повысить скорость связи (и в некоторых случаях освободить ваш DMA быстрее).