Задержка в процессе VHDL между соседними операторами

Я экспериментирую с VHDL и столкнулся с задержкой, от которой я не могу избавиться.

Я пытаюсь запрограммировать очень простой логический вентиль AND с 3 входами на тестовом стенде, который проходит через все возможные входы для AND3 и последующего вывода. Я связал один входной максимум, чтобы упростить его оценку в симуляции.

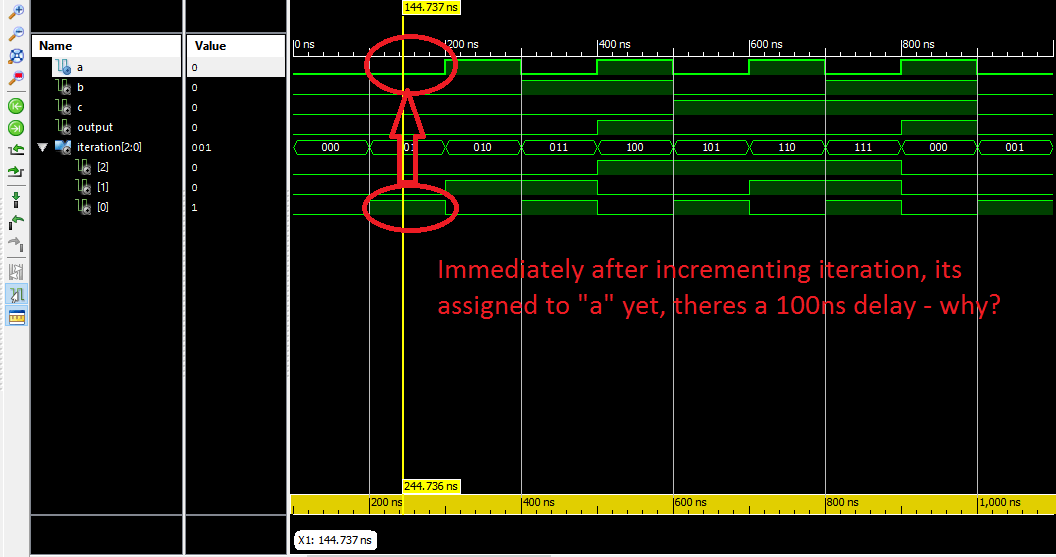

Я запустил симуляцию, которая циклически переключается между 8 значениями для 3 входов (при этом 3-й вход игнорируется), однако, между повторением числа и его назначением входу, несмотря на тот факт, что эти операторы следуют сразу же, есть 100 нс задержка - почему? Задержка в 100 нс между итерациями понятна, поскольку она является преднамеренной, но я не понимаю, почему существует задержка в 100 нс между двумя указанными ниже строками, когда они выполняются последовательно?

Я поставил определение, тестовый стенд ниже,

Спасибо большое!

--ENTITY AND3 (3 input AND gate) --

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity and3 is

port(

a, b, c : in std_logic;

o : out std_logic

);

end entity and3;

architecture RTL of and3 is

begin

o <= (a and b and c) after 5 ns;

end architecture RTL;

--TESTBENCH FOR AND3 with 3rd input left open (tied high)

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity testAnd3 is

end entity testAnd3; -- no ports for a test bench

architecture io of testAnd3 is

component And3 is

port(x, y, z : in std_logic:= '1'; --Sets default value if left open;

o : out std_logic

);

end component And3;

signal a, b, c : std_logic:='0';

signal iteration : unsigned(2 downto 0):= (others => '0');

begin

g1 : And3 port map(x => a, y => b, z => open, o => c); --map signals to And ports

stim_process : process

begin

iteration <= iteration + 1; --//100 ns delay between here and next line!?

a <= iteration(0);

b <= iteration(1);

wait for 100 ns;

end process;

end architecture io;

1 ответ

Проблема заключается в <= назначить в:

iteration <= iteration + 1;

это <= не обновляет прочитанное значение iteration пока после задержки дельта, так что a <= iteration(0); не видит увеличенное значение сразу после, но сначала увидит его на следующей итерации, то есть после wait for 100 ns;,

Это может быть исправлено любым из:

- перемещая назначение в

aа такжеbвне процесса (предлагаемое решение, так как оно соответствует стилю кодирования синтезируемого кода) - перемещение

iteration <= iteration + 1;прямо передwait for 100 ns;посредством чегоwaitбудет "скрывать" задержку обновленияiterationзначение (форма сигнала будет такой же; см. комментарий ниже) - изменения

iterationк локальной переменной вprocess, поскольку переменная присваивается с помощью:=происходит сразу.

Обратите внимание, что задержка обновления сигналов назначена с <= является ключевой характеристикой VHDL, поскольку она гарантирует, что все синхронизированные процессы будут видеть одно и то же значение, независимо от порядка оценки. Подумайте над прочтением этого замечательного ответа: процесс в VHDL реентерабелен?,