Как настроить интерфейс управления для Avalon-MM?

В QSYS у меня есть АЦП, PLL и Avalon-MM Read Master для доступа к внутреннему АЦП Altera Max10. Управление и пользовательский интерфейс Read Master экспортируются.

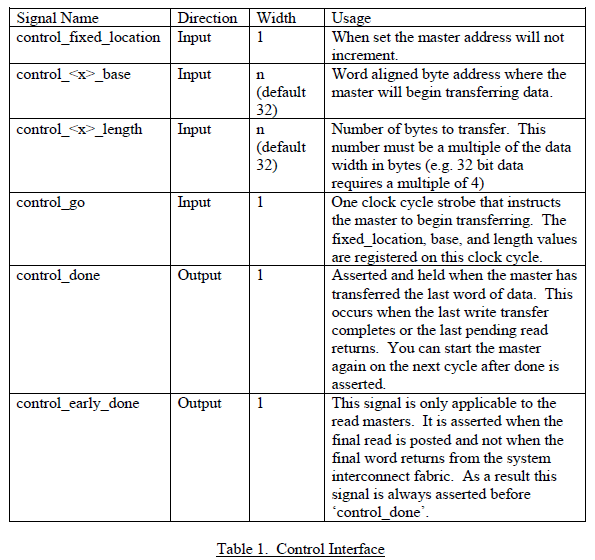

Сейчас я пытаюсь настроить интерфейс управления для доступа к каналам АЦП. В основном следующие сигналы:

- control_fixed_location

- control_read_base

- control_read_length

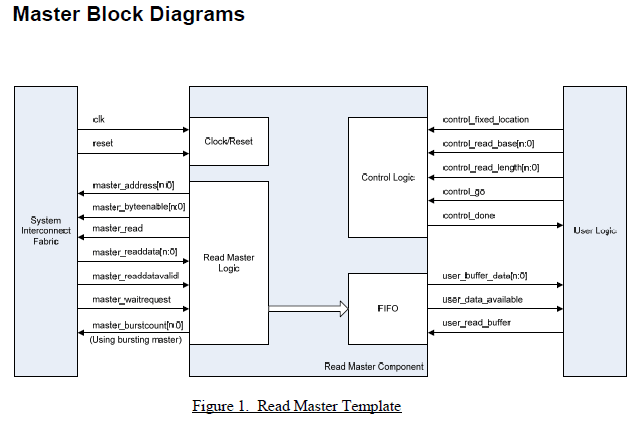

Блок-схема для чтения мастера:

Вопросы: - Как мне установить контрольные сигналы для доступа к каналу АЦП х? - Где я могу найти базовый адрес для АЦП, реализованного в QSYS?

Прилагается архив квартуса. Может быть, кто-то может дать мне пример для моделирования этого интерфейса в ModelSim.

Заранее спасибо!

1 ответ

У меня есть ответ на ваш второй вопрос. Я борюсь с первым вопросом.

Где я могу найти базовый адрес для АЦП, реализованного в QSYS?

Я знаю два метода, чтобы найти базовый и конечный адрес компонента. Один из них - открыть представление " Содержимое системы" (стандартное) и перейти к правой стороне. Я пока не имею права вставлять изображения. Там вы видите строку с именем Base и End. Здесь вы можете найти адреса.

Второй способ - открыть карту адресов. Должен быть расположен в том же столбце, что и Системное содержимое, или вы можете выбрать Вид в левом верхнем углу и выбрать его там. Посмотри. Вы должны быть в состоянии найти это самостоятельно с этой информацией.

То, что я использую, когда я ищу примеры или готовые проекты, - это веб-сайт Altera. Вот ссылка для вас https://cloud.altera.com/devstore/platform/

Вероятно, вам нравится этот: https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/max-10/ug_m10_adc.pdf

Конфигурация завершена в QSYS? Как выбор каналов и секвенсора в вашем блоке АЦП. Выбор правильных входных часов и правильных частот?

Вы писали: В QSYS у меня есть АЦП, ФАПЧ и Avalon-MM Read Master для доступа к внутреннему АЦП Altera Max10. Управление и пользовательский интерфейс Read Master экспортируются.

Вы создали часы для своего PLL? Когда я хочу смоделировать тактовый сигнал для системы QSYS, я экспортирую тактовые сигналы и определяю нужные часы в дополнительном файле.

Если вы сделаете еще один шаг и включите процессор nios2, я рекомендую взглянуть на файл altera_modular_adc.c.

*редактировать

Если вы не назначили никаких базовых адресов, в QSYS есть функция, которая сделает эту работу за вас.

В системе (тот же столбец, что и файл) -> Назначить базовые адреса