Почему этот параллельный оператор менее чем на 100% покрывает код?

Почему следующий оператор генерации часов не покрывает 100% кода в ModelSim/QuestaSim?

clk <= not clk after 5 ns when not finished;

Это полный пример:

library ieee;

use ieee.std_logic_1164.all;

entity coverage1_tb is

end entity;

architecture tb of coverage1_tb is

signal clk : std_logic := '1';

signal finished : boolean := false;

begin -- architecture tb

clk <= not clk after 10 ns when not finished;

--clk <= not clk after 10 ns when not finished else unaffected;

process

begin

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

finished <= true;

wait;

end process;

end architecture;

Если я добавлю эту ветку еще: else unaffectedтогда я получу 100% покрытие.

Параллельное назначение сигналов преобразуется в процессы с последовательными назначениями сигналов (LRM 11.6). Незатронутая ветвь преобразуется в пустой оператор (LRM 11.6, Примечание 2; LRM 10.5.2.1).

Я не уверен, почему ModelSim / QuestaSim требует, чтобы я написал явную ветвь else, которая не содержит форму волны.

2 ответа

Не совсем ответ, но я могу сообщить, что ghdl, созданный с помощью gcc, сообщает о 100% -ном покрытии для этого примера.

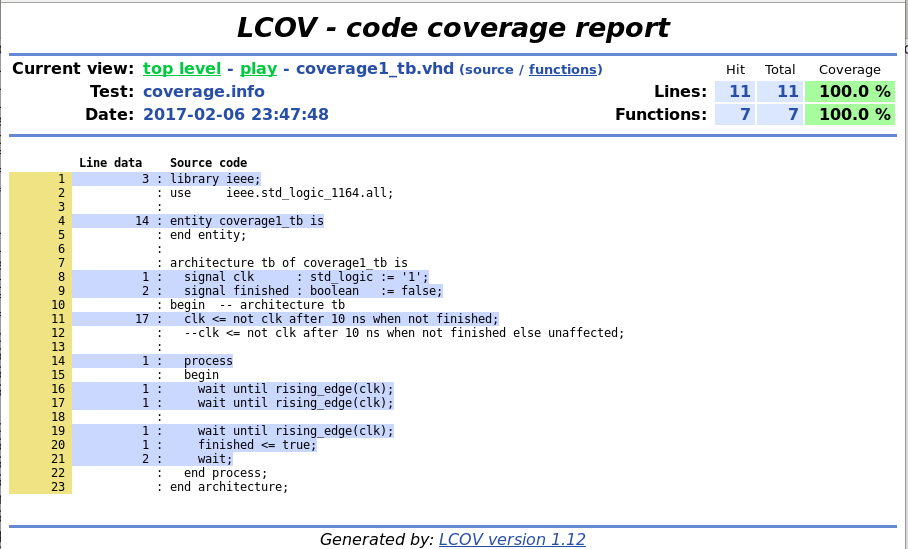

ghdl -a --std=08 -g -fprofile-arcs -ftest-coverage coverage1_tb.vhd

ghdl -e --std=08 -Wl,-lgcov -Wl,--coverage coverage1_tb

./coverage1_tb

lcov --capture --directory .

genhtml coverage.info --output-directory html

Таким образом, это может быть вопросом технической поддержки Modelsim.

Покрытие ветвлений с помощью gcc/ghdl/gcov не столь удовлетворительно: некоторые из более продвинутых конструкций VHDL, такие как назначения сигналов, вовлекают ветви внутри, и gcc не различает эти и фактические ветви в коде VHDL. Таким образом, покрытие филиала работает, но с большим количеством беспорядка. (По иронии судьбы, исключения в C++, профилированные с использованием g++/gcov, по-видимому, сталкиваются с той же проблемой беспорядка).

Какой тип покрытия кода вы имеете в виду? Простое покрытие операторов, или ветвление или переключение покрытия? Для всех этих 3 типов я получаю полное покрытие оператора генерации часов. Может быть, это проблема с более старой версией Modelsim/Questa, которую вы используете? Я использую Modelsim DE 10.6 (Редакция 2016.12).

Мои команды tcl:

vcom -2008 +cover coverage1.vhdl

vsim -novopt -coverage coverage1_tb

run -all