Счетчик VHDL, возвращающий 'X', неизвестное значение

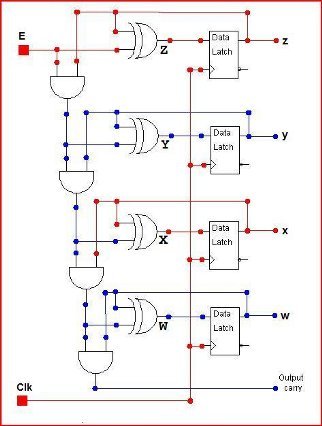

Я пытаюсь создать 4-битный счетчик с созданными экземплярами компонентов, как показано ниже. Когда я симулирую, выход переключается между 0 и X(неизвестный сигнал). Я не уверен, что не так. симуляции, принципиальная схема и код приведены ниже.

4-битный счетчик по модулю

Бит кусочек

library ieee;

use ieee.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use ieee.numeric_std.all;

use IEEE.std_logic_unsigned.all;

--======================================================================

entity counter_BitSlice is

port (

CLK : in std_logic;

En : in std_logic;

reset : in std_logic;

OUTPUT : out std_logic;

AND_En : out std_logic

);

end counter_BitSlice;

--====================================================================

architecture struc of counter_BitSlice is

signal XOr_En : std_logic;

signal En_In : std_logic;

signal Result : std_logic;

begin

counter : process(CLK,XOr_En,reset,Result)

begin

If reset='1' then

XOr_En <='0';

OUTPUT <='0';

AND_En <='0';

Result <='0';

elsif rising_edge(CLK) then

Result <= XOr_En;

end if;

XOr_En <= En_In XOR Result;

AND_En <= En_In AND Result;

OUTPUT <= Result;

En_In <= En;

end process counter;

end struc;

Структурный VHDL

Здесь я использовал команду создания для срезов, но я жестко запрограммировал ее, чтобы устранить ошибки

library ieee;

use ieee.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use ieee.numeric_std.all;

use IEEE.std_logic_unsigned.all;

--======================================================================

entity counter is

generic (

BitLength : natural := 8

);

port (

CLK : in std_logic;

En_In : in std_logic;

reset : in std_logic;

OUTPUT : out std_logic_vector(3 downto 0);

A_carry : out std_logic_vector(3 downto 0)

);

end counter;

--======================================================================

architecture struc of counter is

component counter_BitSlice

port(

CLK : in std_logic;

En : in std_logic;

reset : in std_logic;

AND_En : out std_logic;

OUTPUT : out std_logic

);

end component;

--======================================================================

signal AND_En_carry : std_logic_vector(3 downto 0);

signal OUTPUT_carry : std_logic_vector(3 downto 0);

begin

--======================================================================

--CCHV_gen : for i in 1 to (BitLength) generate

--begin

CCHV_1 : counter_BitSlice

port map(

CLK => CLK,

reset => reset,

En => En_In,

AND_En => AND_En_carry(0),

OUTPUT => OUTPUT_carry(0)

);

CCHV_2 : counter_BitSlice

port map(

CLK => CLK,

reset => reset,

En => AND_En_carry(0),

AND_En => AND_En_carry(1),

OUTPUT => OUTPUT_carry(1)

);

CCHV_3 : counter_BitSlice

port map(

CLK => CLK,

reset => reset,

En => AND_En_carry(1),

AND_En => AND_En_carry(2),

OUTPUT => OUTPUT_carry(2)

);

CCHV_4 : counter_BitSlice

port map(

CLK => CLK,

reset => reset,

En => AND_En_carry(2),

AND_En => AND_En_carry(3),

OUTPUT => OUTPUT_carry(3)

);

-- end generate CCHV_gen;

OUTPUT <= OUTPUT_carry;

A_carry <= AND_En_carry;

main : process(reset, CLK)

begin

if rising_edge(CLK) then

if reset ='1' then

AND_En_carry <= (others=>'0');

OUTPUT_carry <= (others =>'0');

end if;

end if;

end process;

end architecture struc;

Испытательный стенд для кусочков битов

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use IEEE.std_logic_unsigned.all;

entity tb_counter_BlitSlice is

end tb_counter_BlitSlice;

architecture tb_behav of tb_counter_BlitSlice is

component counter_BlitSlice

port(

CLK : in std_logic;

En : in std_logic;

reset : in std_logic;

OUTPUT : out std_logic;

AND_En : out std_logic

);

end component;

constant t_BitLength : natural :=8;

signal t_En :std_logic := '0';

signal t_CLK : std_logic :='0';

signal t_reset : std_logic :='0';

signal t_OUTPUT : std_logic :='0';

signal t_AND_En : std_logic :='0';

begin

U1: counter_BlitSlice

port map (

CLK => t_CLK,

reset => t_reset,

En => t_En,

OUTPUT => t_OUTPUT,

AND_En => t_AND_En

);

t_CLK <= not t_CLK after 20 ns;

test : process

begin

t_En <= '0';

t_reset <='0';

wait for 20 ns;

t_reset <='1';

wait for 20 ns;

t_reset <='0';

wait for 20 ns;

t_En <= '0';

wait for 40 ns;

t_En <= '1';

wait for 20 ns;

wait;

end process test;

end architecture tb_behav;

Испытательный стенд для счетчика

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_unsigned.all;

entity tb_counter is

end tb_counter;

architecture tb_behav of tb_counter is

component counter

generic(

BitLength : natural :=8

);

port(

CLK : in std_logic;

En_In : in std_logic;

reset : in std_logic;

OUTPUT : out std_logic_vector(3 downto 0);

A_carry : out std_logic_vector(3 downto 0)

);

end component;

constant t_BitLength : natural :=8;

signal t_En :std_logic := '0';

signal t_CLK : std_logic :='0';

signal t_reset : std_logic :='0';

signal t_OUTPUT : std_logic_vector(3 downto 0) := (others =>'0');

signal t_ANDcarry : std_logic_vector(3 downto 0) := (others =>'0');

begin

U1: counter

generic map(

BitLength => t_BitLength

)

port map (

CLK => t_CLK,

reset => t_reset,

En_In => t_En,

OUTPUT => t_OUTPUT,

A_carry => t_ANDcarry

);

t_CLK <= not t_CLK after 20 ns;

test : process

begin

t_En <= '0';

t_reset <='0';

wait for 20 ns;

t_reset <='1';

wait for 80 ns;

t_reset <='0';

wait for 60 ns;

t_En <= '0';

wait for 40 ns;

t_En <= '1';

wait for 20 ns;

wait;

end process test;

end architecture tb_behav;

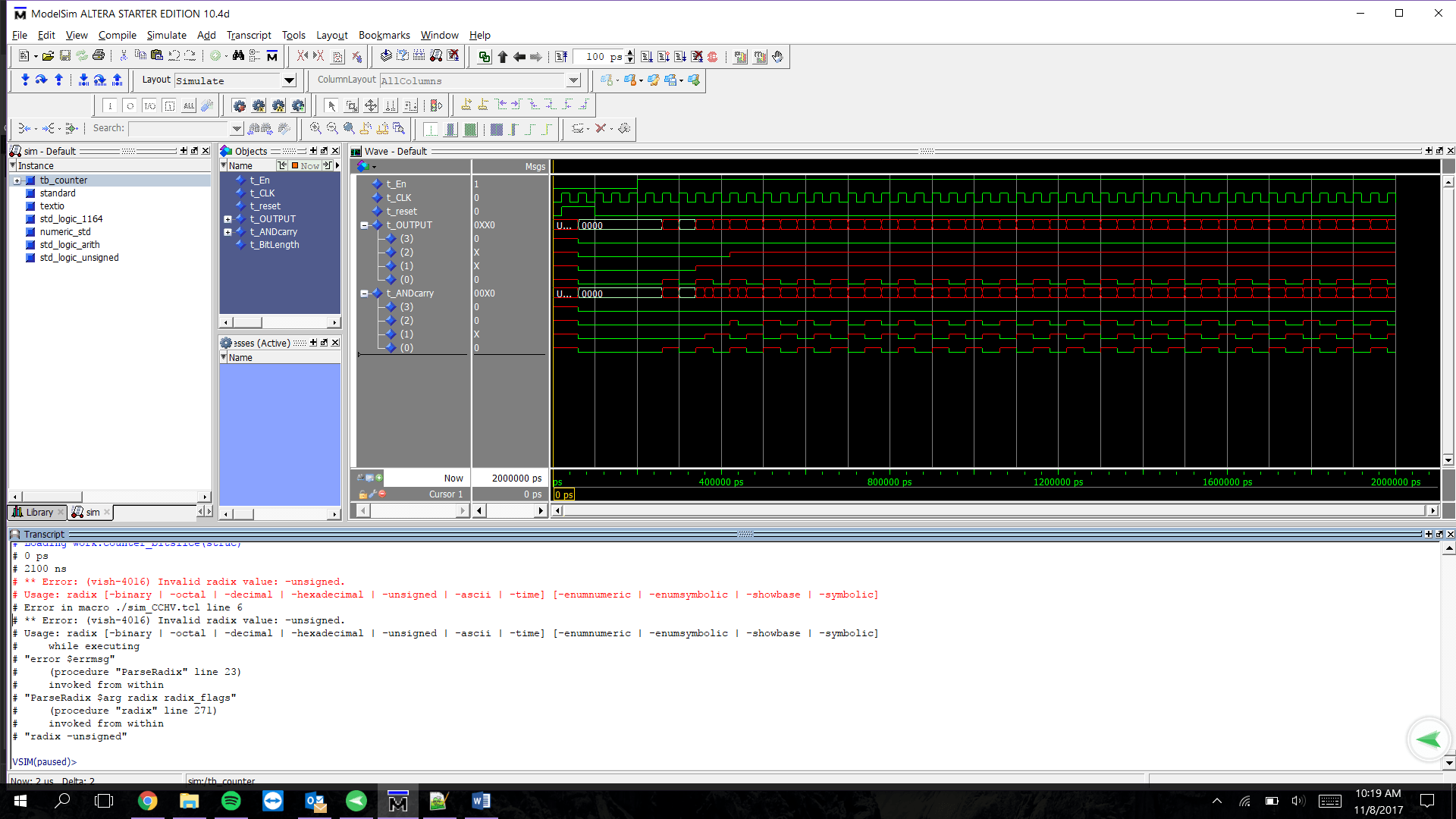

Когда я симулирую битовый срез, выход переключается правильно, как показано ниже.

Битовая часть симуляции счетчика

И когда я имитирую комбинированный счетчик, чтобы получить четырехбитный счетчик, он переключается между значением без знака, как показано ниже. Я не понимаю, в чем проблема.

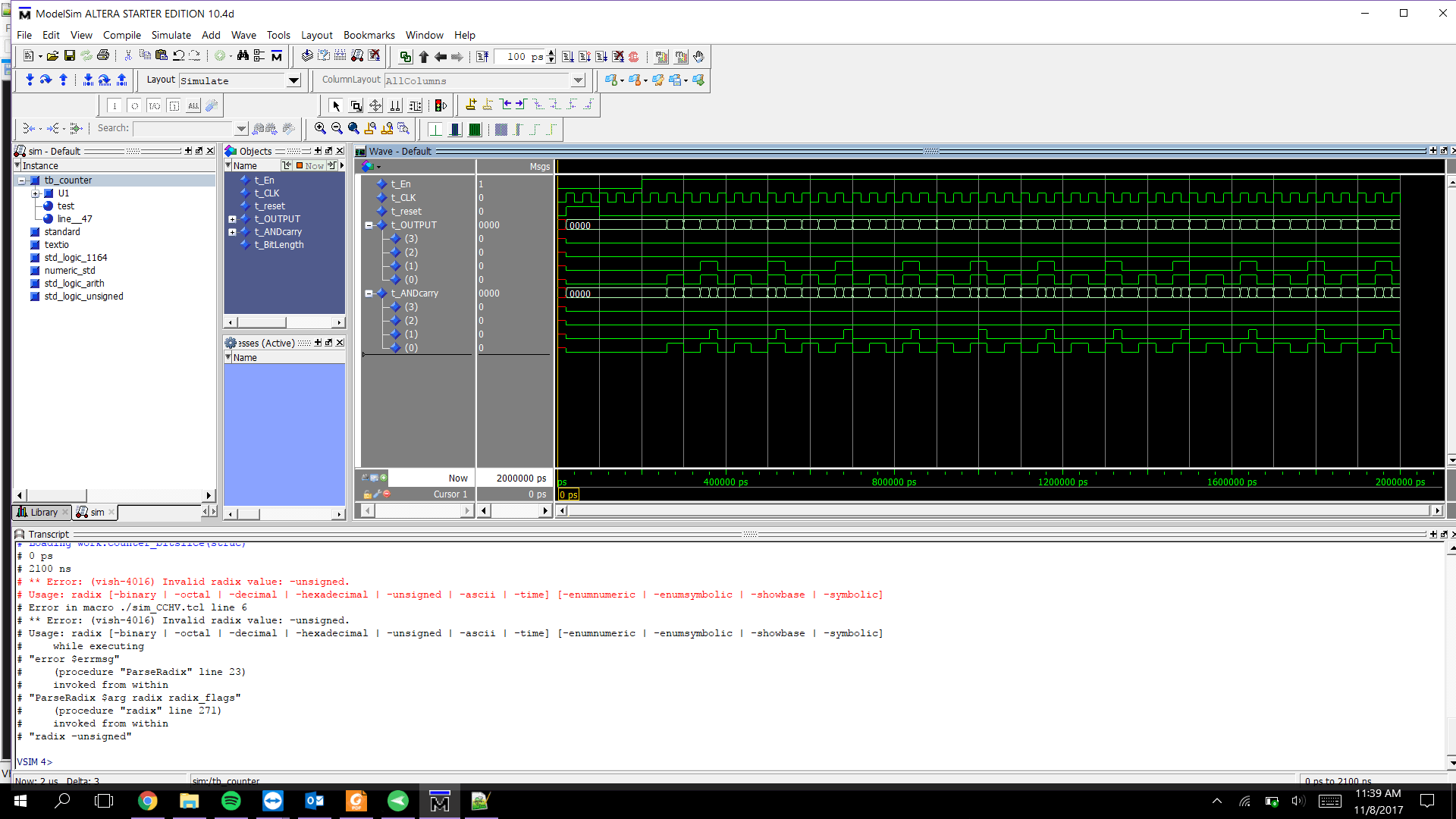

2:

Я удалил сброс в файле control.vhd, и тот избавился от неизвестного сигнала, но он не считается правильно. как кажется ниже.

1 ответ

Я получил его после изменения кода slice_counter.

counter : process(CLK,reset)

begin

If reset='1' then

OUTPUT <='0';

Result <='0';

elsif rising_edge(CLK) then

OUTPUT <= XOr_En;

Result <= XOr_En;

end if;

end process counter;

XOr_En <= En XOR Result;

AND_En <= En AND Result;

end struc;

Вы должны были поставить ворота AND и XOR вне процесса. Это было причиной ошибки.