Конфигурирование чипа ракеты

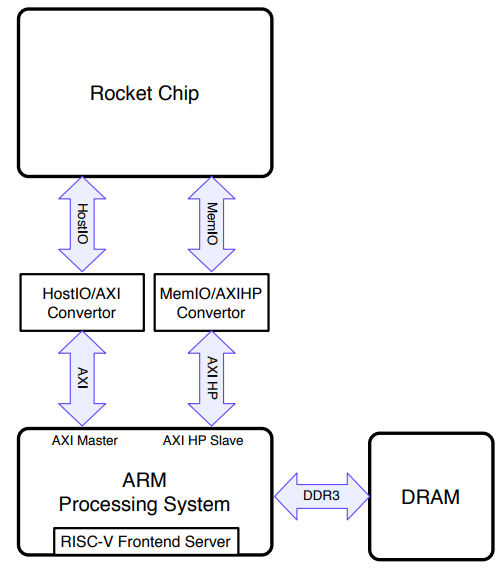

Я хочу создать свой собственный SOC на основе чипа ракеты без использования ROCC(сопроцессор руки). Я проверил этот полезный вопрос: ракетный чип на не Zynq FPGA Я искал некоторую подробную документацию, но я нашел только несколько слайдов, описывающих конфигурации без фактического учебника. Таким образом, у меня есть три вопроса относительно изображения ниже:

- Мне удалось сгенерировать общий verilog для tinyConfig, но возможно ли сгенерировать только Rocket Chip, HostIO/AXI Convertor и MemIO/AXIHP Convertor? если да как?

- Может ли интерфейс отладки быть добавлен ракетным генератором чипов?

- Где я могу изменить оперативную память, используемую в ракете, оперативной памятью определенного производителя ПЛИС?

0 ответов

Verilog, генерируемый ракетным чипом, может использоваться в FPGA. Вам просто нужно заменить behavior_srams.v оперативной памятью, созданной в vivado.

В system/Config.scala вы можете добавить класс WithJtagDTMSystem в свою конфигурацию для создания интерфейса отладки.