Каковы точные критерии для входного порта, когда иногда входной и выходной порты могут быть взаимозаменяемо использованы в Verilog?

В приведенном ниже модуле в идеале cnt, width & start должен быть входным портом, а не выходным.

Но я попытался использовать эти порты в качестве выходных, и все же я могу запустить его без каких-либо ошибок. Так могут ли входной и выходной порты использоваться в Verilog взаимозаменяемо?

Если нет, то каковы точные критерии, где должен использоваться входной порт (выходной порт не может использоваться в этом случае)?

module (clk, rst, cnt, start, width, signal);

input clk, rst, signal;

output reg [11:0] cnt, width;

output reg start;

always @(posedge clk or negedge rst)

begin

if(~rst)

begin

cnt <= 0;

start = 0;

width <= 'h271;

end

else

begin

if(signal)

begin

width <= (start) ? width : 'h271;

start = 1;

end

cnt <= (start) ? (cnt + 1) : cnt;

end

end

endmodule

Примечание. Я знаю, что при использовании портов inout мне нужно изменить код, так как порты inout не могут иметь тип reg. Но я здесь спрашиваю только о типе портов.

3 ответа

Направление порта в Verilog носит рекомендательный характер, а в SystemVerilog это не изменилось. Это исторический вопрос, связанный с тем, как Verilog XL (первый симулятор Verilog) делал коллапс порта; в принципе, все является inout. когда была написана LRM '95, это существующее поведение было в основном задокументировано. В 1364-2005 это появляется в 12.3.8 как

Порт, который объявлен как вход (выход), но используется как выход (вход) или inout, может быть принудительно установлен как inout. Если не принужден к вводу, должно быть выдано предупреждение.

На практике все заканчивается как inoutи вы можете или не можете получить предупреждение. Таким образом, вы можете делать практически все в симуляторе, но линтер или синтезатор должны выявлять любые логические ошибки соединения для вас (если это не так, это довольно бесполезно). В следующих разделах есть другие конкретные правила ненаправления input а также inout порты должны быть net типа и тд.

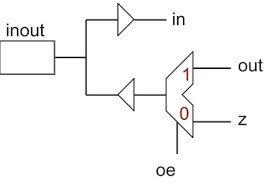

Есть различия в output а также inout порты:

Вы не можете читать и писать

inoutпорт одновременно, следовательно, сохраняется'Zдля чтения.inoutпорт никогда не может быть типаreg, Это должно бытьwireтип.Должен быть сигнал, который решает, является ли данный порт

inputили жеoutput,

В этом модуле вы должны иметь w_r сигнал, который работает следующим образом:

// w_r = 1 => output port

// w_r = 0 => input port

input w_r;

inout cnt;

reg write_cnt;

reg read_cnt;

// wire read_cnt;

assign cnt = w_r ? write_cnt : 1'bz; // driving logic for cnt

// inside some always block

read_cnt <= cnt;

write_cnt <= some_data;

Так как inout Сигнал является проводным, он должен управляться непрерывными операторами присваивания.

Ссылаясь на эту часть:

Так могут ли входной и выходной порты использоваться в Verilog взаимозаменяемо?

Ответ заключается в том, что не рекомендуется использовать их взаимозаменяемо. Так как для выходного порта вы можете использовать reg введите один.

С точки зрения синтеза inout Порт может иметь драйверы с тремя состояниями или Mux следующим образом: (Обратите внимание, что эти результаты могут отличаться для инструментов синтеза, в которых я не уверен.):

Для получения дополнительной информации обратитесь к разделу форума " Двунаправленное назначение портов" и " Двунаправленные выводы ввода / вывода".

Симуляторы не заботятся о направлениях портов. Инструменты моделирования всегда сглаживают иерархию модулей, и все, что имеет значение, - это то, что они могут соединять сигналы двух портов вместе. Они не проверяют, что поток данных действительно идет в указанном направлении. К сожалению, то, что требуется стандартом и что реализовано в инструменте, не всегда совпадает.

Иногда у пользователя будет код, который "работает" в одном инструменте, но не в другом инструменте с более сильной проверкой ошибок. Пользователь обнаруживает, что его поставщику инструментов легче убрать проверку ошибок, чем возвращаться и исправлять свой код. Некоторые большинство симуляторов убрали все проверки, чтобы обеспечить направление порта.

Правило о том, чтобы не объявлять переменные типы данных, используемые во входных портах, остается в основном неизменным, но многие инструменты позволяют подключать константы к входному порту.