8-битный микроконтроллер PicoBlaze с инструкциями по переходу и вызову

Я студент, и мне нужно создать 8-битный микроконтроллер PicoBlaze на основе этой документации XAPP213.

У меня проблема, когда мне нужно выполнить команду перехода или вызова:

Когда я прыгаю или вызываю следующую инструкцию, я вынужден быть NULL-инструкцией, и, таким образом, мой счетчик программ (ведьма дает мне мой новый АДРЕС) остается в том же значении, что он держит в течение 2 часов один и тот же адрес, и для этого два раза читает инструкцию на ведьма я прыгнул или я позвонил.

Что я могу сделать, чтобы не допустить этого?

Вот мой код счетчика программ, если он помогает:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

use IEEE.NUMERIC_STD.all;

entity DL_PROGRAM_COUNTER is

port(

SELECT_1 : in BIT;

SELECT_0 : in BIT;

CARRY_IN : in BIT;

CLK : in BIT;

RESET : in BIT;

ADR : in BIT_VECTOR(7 downto 0);

IESIRE_STACK : in BIT_VECTOR(7 downto 0);

ADDRESS : out BIT_VECTOR(7 downto 0)

);

end DL_PROGRAM_COUNTER;

--}} End of automatically maintained section

architecture DL_A_PROGRAM_COUNTER of DL_PROGRAM_COUNTER is

component DL_GENERIC_MUX is

generic (Numar_biti_selectie: NATURAL :=1; Numar_biti_cale_date: NATURAL:=1);

port (date: in BIT_VECTOR(0 to (2**Numar_biti_selectie)*Numar_biti_cale_date - 1); -- date <= a0 & a1

sel: in BIT_VECTOR(Numar_biti_selectie-1 downto 0);

Y: out BIT_VECTOR(Numar_biti_cale_date-1 downto 0)

);

end component;

component DL_GENERIC_REGISTRU_PASTRARE is

port(date: in BIT_VECTOR(7 downto 0);

clk,ce,reset: in BIT;

Q: out BIT_VECTOR(7 downto 0)

);

end component;

signal intermediar,iesire_1,iesire_0,aresa_urmatoare: BIT_VECTOR(7 downto 0);

signal date1,date0: BIT_VECTOR(0 to 15);

signal sel1,sel0: BIT_VECTOR(0 downto 0);

begin

COPIERE1: process(intermediar,ADR)

begin

for k in 0 to 7 loop

date1(k) <= intermediar(7-k);

date1(8+k) <= ADR(7-k);

end loop;

end process;

sel1(0) <= SELECT_1;

MUX1: DL_GENERIC_MUX generic map(1,8) port map(date1,sel1,iesire_1);

COPIERE0: process(iesire_1,IESIRE_STACK)

begin

for k in 0 to 7 loop

date0(k) <= iesire_1(7-k);

date0(8+k) <= IESIRE_STACK(7-k);

end loop;

end process;

sel0(0) <= SELECT_0;

MUX2: DL_GENERIC_MUX generic map(1,8) port map(date0,sel0,iesire_0);

ADDER:process(iesire_0,CARRY_IN)

variable rez: INTEGER;

begin

rez := CONV_INTEGER(TO_STDLOGICVECTOR(iesire_0));

if CARRY_IN = '1' then

rez := rez + 1;

end if;

aresa_urmatoare <= TO_BITVECTOR(STD_LOGIC_VECTOR(TO_UNSIGNED(rez, aresa_urmatoare'length)));

end process;

REGISTRU: DL_GENERIC_REGISTRU_PASTRARE port map(aresa_urmatoare,CLK,'1',RESET,intermediar);

ADDRESS <= intermediar;

end DL_A_PROGRAM_COUNTER;

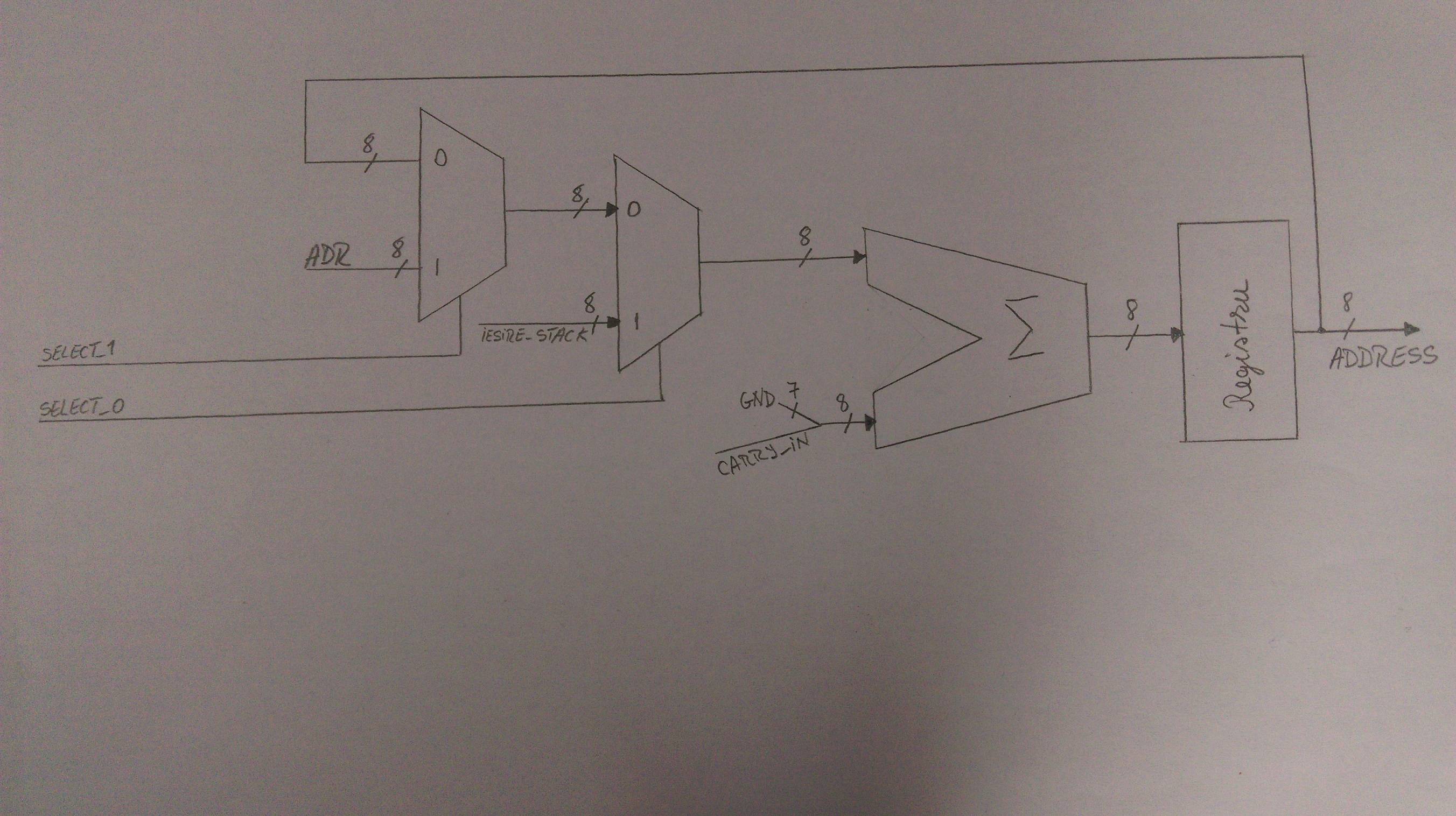

Вот блок-схема того, как это выглядит:

для прыжка:

select_1 <= '1';

select_0 <= '0';

carry_in <= '0';

для вызова:

select_1 <= '1';

select_0 <= '0';

carry_in <= '0';

для NULL-инструкции:

select_1 <= '0';

select_0 <= '0';

carry_in <= '0';