Verilog Simulation: разное поведение, одно и то же состояние

Я проектирую процессор на плате Alteras DE1, и ради него я решил использовать JAVA BYTECODES в качестве набора инструкций.

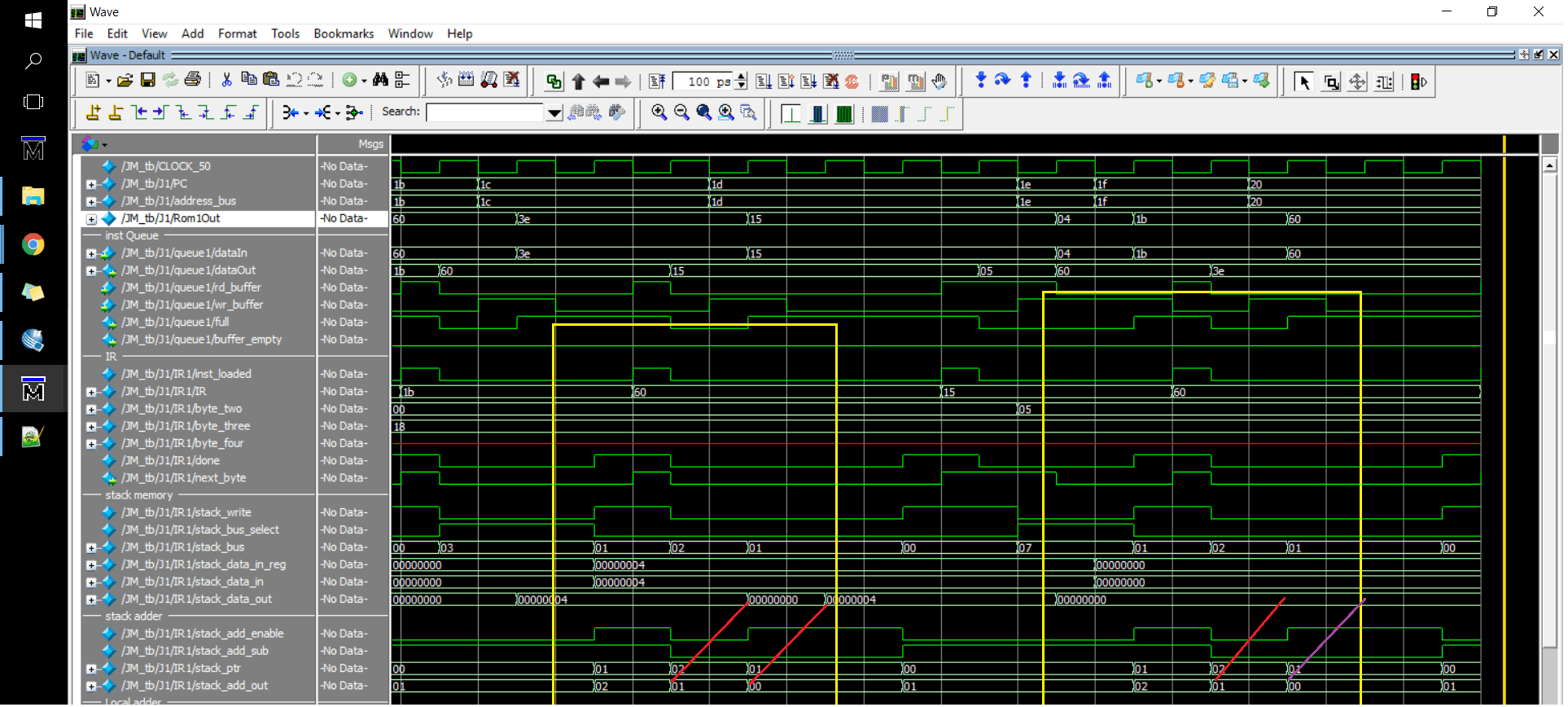

Проблема в том, что когда инструкция iadd приходит, я получаю два разных поведения, область стека, которая является мегафункцией altsyncram с шириной 32 и глубиной 64, не выводит данные. Я проверил все шины и сигналы управления и их значения, кажется, правильные.

красные линии указывают на изменение адресной шины, что приводит к изменению отображаемых данных, но фиолетовая линия - там, где проблема. данные должны измениться на h00000004, но это не так.

как видите все условия одинаковы.

Код, связанный с ним:

stack_write = 1'b0; // read stack_area

stack_bus_select = 1'b0; // stack_bus = stack_ptr

stack_add_sub = 1'b0; // stack incrementer/decrementor = decrement

stack_add_enable = ~stack_add_enable; // enable stack adder

stack_ptr = stack_add_out;

wait(!clock);

wait(clock);

long_A = {{32{stack_data_out[31]}}, stack_data_out[31:0]};

stack_add_sub = 1'b0;

stack_add_enable = ~stack_add_enable;

stack_ptr = stack_add_out;

wait(!clock);

wait(clock);

long_B = {{32{stack_data_out[31]}}, stack_data_out[31:0]};

ALU_operation = 3'b100;

wait(!clock);

wait(clock);

stack_data_in_reg = result;

stack_write = 1'b1; // write stack_area

stack_bus_select = 1'b0; // stack_bus = stack_ptr

stack_add_sub = 1'b1;

stack_add_enable = ~stack_add_enable;

stack_ptr = stack_add_out;

done = 1'b1;

PS: Я новичок в Verilog и FPGA в целом. Так что любые предложения приветствуются.