Настройте тактовый сигнал для черного ящика в Simulink/System Generator

Я использую код VHDL, чтобы сделать однократный таймер в Simulink "черным ящиком" System Generator. Модуль заключает, что вход: clk, en, триггер, задержка и выход: плюс. Теперь я хочу использовать System Generator для реализации на Zynq 7020 и использовать тактовую частоту = 1.562 МГц. Я прочитал "ug897-vivado-system generator-user", но я все еще не знаю, как настроить clk.

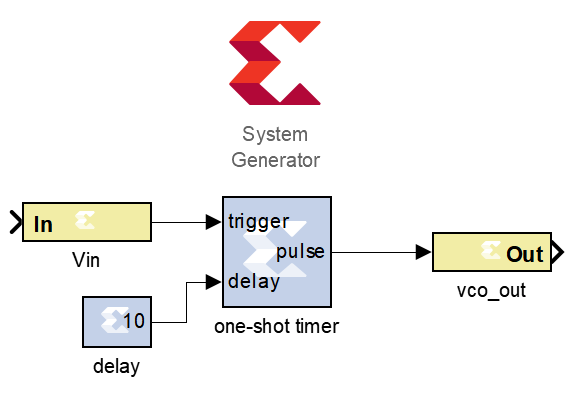

Диаграмма в Матлаб / Симулинк

Код VHDL для одноразового таймера / черного ящика

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

library UNISIM;

use UNISIM.VComponents.all;

entity oneshot is

port ( clk : in STD_LOGIC;

ce : in STD_LOGIC;

trigger : in STD_LOGIC:='0';

delay : in STD_LOGIC_VECTOR (7 downto 0);

pulse : out STD_LOGIC :='0');

end oneshot;

architecture Behavioral of oneshot is

signal count: INTEGER range 0 to 255; -- count variable

signal bus_rising_edge : boolean;

signal input_sync : std_logic_vector(0 to 2);

begin

input_syncronizer : process(clk) begin

if rising_edge(clk) then

input_sync <= to_x01(trigger)&input_sync(0 to 1);

end if;

end process ;

bus_rising_edge <= input_sync(0 to 1) = "10";

trigger_process: process (clk)

begin

-- wait for trigger leading edge

if rising_edge(clk) then

if bus_rising_edge then

pulse <= '1';

count <= to_integer(unsigned(delay));

elsif count > 1 then

pulse <= '1';

count <= count - 1;

else

pulse <= '0';

end if;

end if;

end process;

end Behavioral;

Код Matlab автоматически создается при импорте кода VHDL https://drive.google.com/open?id=1jfztL-NgftDc7VAgAX4eHfuJF8uOgK3V

(извините, я не могу опубликовать свой код правильно)

1 ответ

Вы можете дважды щелкнуть по значку генератора системы и выбрать вкладку синхронизации и изменить период ваших часов. эти часы используются для моделирования. на самом деле ваши рабочие часы - это то, что у вас на доске.