VHDL-кодирование: 10-битное десятичное преобразование в BCD возможно ли?

Хорошего дня,

Мое последнее назначение - преобразовать 10-битное десятичное число (поскольку максимальное десятичное число 10-битного составляет 1023) в 16-битное BCD. Когда десятичный входной сигнал больше или равен 1024, тогда сигнал ошибки будет высоким. Весь модуль, конечно, связан с часами. Я не знаю, как я могу реализовать это в кодировании VHDL, но у меня есть несколько предложенных идей о том, как я могу заставить это работать:

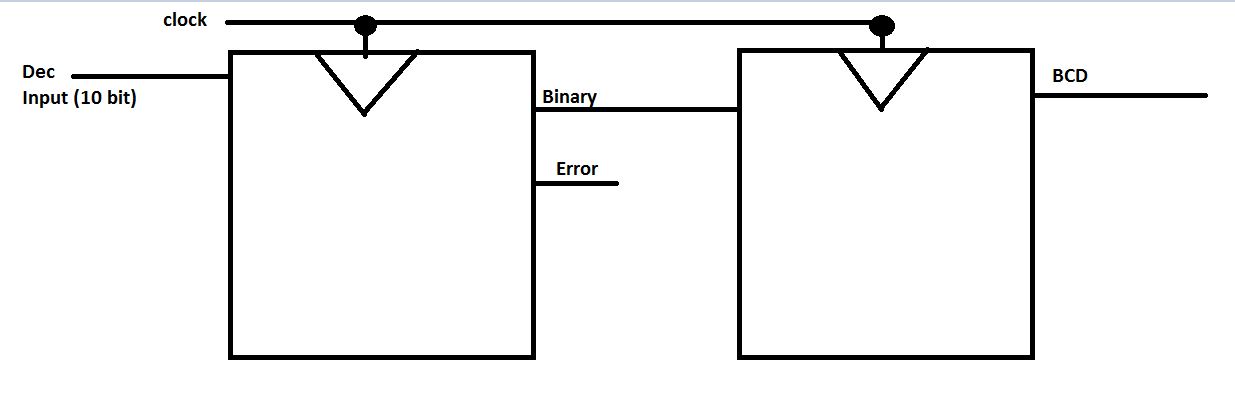

- Во-первых, я мог бы реализовать использование ДВУХ МОДУЛЕЙ, когда выход первого блока будет подключен ко второму блоку с такими же часами. Выход первого блока является двоичным входом, где ошибка равна 1, когда десятичный вход больше 1023.

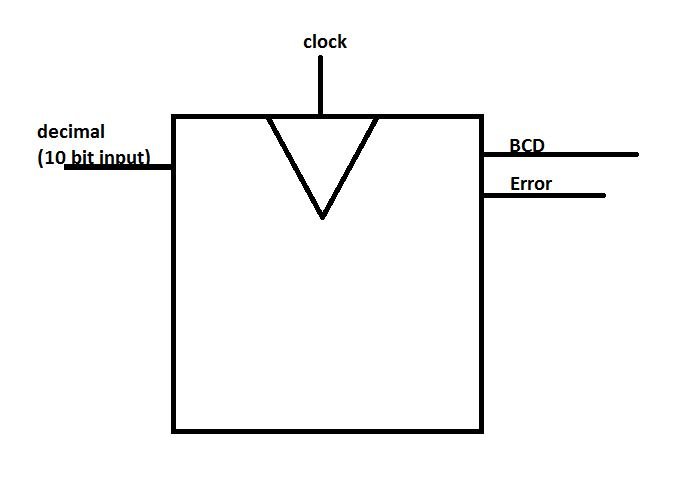

- Второй - просто использовать метод одного модуля, в котором входная десятичная дробь напрямую преобразуется в 16-разрядный BCD, где ошибка равна единице, если входная десятичная дробь больше 1023.

Может кто-нибудь помочь мне о том, как закодировать десятичное преобразование в BCD с помощью VHDL. Небольшая помощь очень ценится. Спасибо

2 ответа

Вы можете использовать алгоритм Double dabble для этой цели. Для этого я написал в своем блоге функцию vhdl, которая в основном преобразует 8-битный двоичный код в 12-битный BCD. Вы можете использовать ту же концепцию и для 10-битных двоичных чисел.

function to_bcd ( bin : std_logic_vector(7 downto 0) ) return std_logic_vector is

variable i : integer:=0;

variable bcd : std_logic_vector(11 downto 0) := (others => '0');

variable bint : std_logic_vector(7 downto 0) := bin;

begin

for i in 0 to 7 loop -- repeating 8 times.

bcd(11 downto 1) := bcd(10 downto 0); --shifting the bits.

bcd(0) := bint(7);

bint(7 downto 1) := bint(6 downto 0);

bint(0) :='0';

if(i < 7 and bcd(3 downto 0) > "0100") then --add 3 if BCD digit is greater than 4.

bcd(3 downto 0) := bcd(3 downto 0) + "0011";

end if;

if(i < 7 and bcd(7 downto 4) > "0100") then --add 3 if BCD digit is greater than 4.

bcd(7 downto 4) := bcd(7 downto 4) + "0011";

end if;

if(i < 7 and bcd(11 downto 8) > "0100") then --add 3 if BCD digit is greater than 4.

bcd(11 downto 8) := bcd(11 downto 8) + "0011";

end if;

end loop;

return bcd;

end to_bcd;

Код тоже можно синтезировать.

Ну, мой одноклассник выяснил проблему, как закодировать это с помощью функции MOD. Вот код:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dec_to_bcd is

Port ( Ina : in STD_LOGIC_VECTOR (9 downto 0);

clk : in STD_LOGIC;

Outa : out STD_LOGIC_VECTOR (15 downto 0);

err : out STD_LOGIC);

end dec_to_bcd;

architecture Behavioral of dec_to_bcd is

begin

process (clk)

begin

if clk='1' and clk'event then

if (conv_integer(Ina) >= 1024) then

err <= '1';

else

Outa(15 downto 12) <= conv_std_logic_vector((conv_integer(Ina) / 1000),4);

Outa(11 downto 8) <= conv_std_logic_vector((conv_integer(Ina) / 100)MOD 10,4);

Outa(7 downto 4) <= conv_std_logic_vector((conv_integer(Ina) / 10)MOD 10,4);

Outa(3 downto 0) <= conv_std_logic_vector((conv_integer(Ina))MOD 10,4);

end if;

end if;

end process;

end Behavioral;

Поскольку наше введение в VHDL в классе использует только симуляцию, мы не знаем, является ли оно "синтезируемым". Любые предложения по улучшению этого кода приветствуются. Спасибо:)