Странный компонент в Quartus RTL Viewer с использованием Verilog

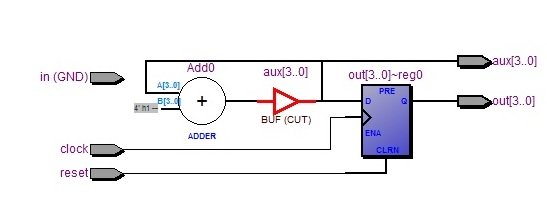

Я изучаю verilog, и когда я не знаю, как будет работать схема, просто просматривая код verilog, я иду в RTL Viewer, чтобы увидеть цифровую логику. Но в этом коде появляется странный компонент, и я не знаю, что это за компонент. Это триггер, мультиплексор или логический порт? ниже код и изображение, на изображении компонент - красный треугольник.

Код:

module testesoma(clock,reset,in, out,aux);

input wire reset, clock, in ;

output reg [3:0] out,aux;

always @(posedge clock or posedge reset)

begin

if(reset)

begin

out = 0;

end

else

out = aux;

aux = aux + 1;

end

endmodule

2 ответа

Какая замечательная схема: +1 за то, что потратил время на ее создание. У вас есть несколько проблем с вашим кодом, и это отличный пример опасности использования блокирующих заданий, обратной связи, не использования шаблонов синтеза и так далее. Quartus, конечно, облажался, но это не удивительно, учитывая ввод. Вопросы:

- не используйте блокирующие назначения здесь - используйте

<= - разбери свой

beginс иends. В качестве отправной точки, не ставьтеbegin/endв вашем коде, если в этом нет необходимости; это многословно, и скрывает ошибки, подобные этой. Использовать толькоbegin/endкогда вам явно нужно сделать многоступенчатый блок. Обратите внимание, чтоaux=aux+1вне твоих часовif/elseутверждение - когда это должно исполниться? - Разберись где и когда хочешь

auxувеличить. - Будьте очень осторожны, когда у вас есть отзывы, как

aux=aux+1, Если вы не будете осторожны, реальное оборудование будет колебаться. - не пишите такую логическую цепочку - начните думать параллельно.

У Quartus был довольно хороший ход, но созданная им схема будет просто колебаться, и aux выход не синхронизирован, что, по-видимому, было вашим намерением. Quartus поместил красный буфер, потому что он может видеть, что он создал нестабильную цепь обратной связи, и у него было нерешительное движение, чтобы сломать его. Это должно было произвести предупреждение где-то об этом.

1 - переписать свой код; что-то вроде

always @(posedge clock or posedge reset)

if(reset)

out <= 0;

else

out <= aux;

always @(posedge clock or posedge reset)

if(reset)

aux <= 0;

else

aux <= aux + 1'b1;

2 - не присваивать нескольким переменным в такте always до тех пор, пока вы не поймете, что может пойти не так (подсказка: проверьте все ветви / пути выполнения, убедитесь, что со всеми переменными, которые вы назначаете во всех возможных путях, происходит что-то логическое)

3 - Найдите книгу по VHDL, прочитайте главу о задержках / назначениях дельты, и ваш Verilog будет намного лучше.

Этот символ является просто буфером, который управляет выводом, равным вводу. Относительно того, почему это появилось бы в цифровой логической схеме, я не уверен.

Буферы не влияют на цифровое функционирование схемы, они вставляются синтезаторами, когда емкость сети слишком велика для эффективной работы ячейки драйвера. Вы можете в основном игнорировать это.

Также я немного подозрительно отношусь к этой схеме, она не соответствует вашему RTL. RTL увеличивает aux на каждом такте, но это показывает комбинационную петлю обратной связи через сумматор, которая, похоже, не будет работать вообще.