Как сделать простое моделирование Aldec Active-HDL с осциллограммой с использованием сценариев Tcl?

Наличие простого тестового стенда, как:

entity tb is

end entity;

architecture syn of tb is

signal show : boolean;

begin

show <= TRUE after 10 ns;

end architecture;

Графический интерфейс ModelSim позволяет моделировать и просматривать кривые с помощью сценария Tcl в "all.do" с:

vlib pit

vcom -work pit tb.vhd

vsim pit.tb

add wave sim:/tb/show

run 20 ns

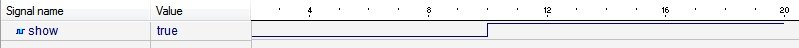

Куда do all.do в консоли GUI ModelSim создаст библиотеку, скомпилирует, загрузит модель t b и покажет форму волны:

Как сделать аналогичный простой сценарий Tcl для аналогичного моделирования с помощью симулятора Aldec Active-HDL?

1 ответ

Документация Aldec Active-HDL для использования Tcl довольно расплывчата в том, как использовать Tcl из графического интерфейса, но достаточное количество времени с пробами и ошибками дало положительный результат.

Похоже, что необходимо создать рабочее пространство с дизайном, посредством чего также создается библиотека для работы, а затем файлы дизайна могут быть скомпилированы в библиотеку.

В результате получается Tcl-скрипт для Active-HDL:

workspace create pit # Create workspace namded "pit" and open this

design create -a pit . # Create design named "pit" with "pit" library as work and add to workspace

acom $DSN/../tb.vhd # Compile "tb.vhd" file with location relative to workspace

asim work.tb # Load simulator from work library

add wave /tb/show # Add wave "show" to waveform

run 20 ns # Simulate 20 ns

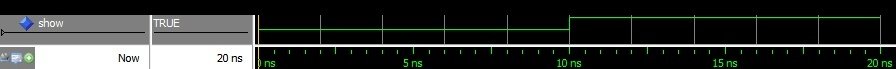

Который даст форму волны: