Отправка данных с медленного домена часов на быстрый

Предположим, я хочу отправить поток данных из медленного домена в быстрый домен, и задержка важна. Есть ли какой-нибудь способ установить нижнюю границу задержки?

Стандартным решением является FIFO, и его задержка обеспечит жесткую верхнюю границу. Кажется очевидным, что данные необходимо будет зарегистрировать в обоих доменах, и потребуется некоторое время, чтобы разрешить путь между доменами и метастабильность. Я, вероятно, могу реализовать FIFO, который не имеет никаких накладных расходов сверх этого, хотя его временные ограничения было бы проблематично задавать (и, возможно, встретить). Я, конечно, могу сделать это безопасно, учитывая один дополнительный цикл в получающем домене.

Однако "кажется ясным" не является чугунным аргументом. Может быть, есть неочевидная реализация, которая не предполагает соединения двух синхронных цепей вместе. Это кажется длинным выстрелом, так что, возможно, есть какой-то строгий аргумент, который обеспечит жесткую нижнюю границу задержки? Большое спасибо.

Изменить: когда я говорю нижнюю границу, я имею в виду наименьшее количество времени, которое должно занять любое правильное решение проблемы, а не задержка какой-либо конкретной реализации. Аналогия: суммирующий переносчик имеет задержку O(n), и это верхняя граница стоимости сложения двух двоичных чисел (потому что мы знаем, как сделать это с такой скоростью, поэтому проблема может быть не сложнее). Мы также знаем, что двоичное добавление должно занимать время Omega(log(n)), потому что старший бит будет зависеть от 2n входов (и лучшее, что мы можем сделать, - это построить дерево с этими входами на листьях).

1 ответ

Несколько комментариев, прежде чем я попытаюсь ответить:

Если вы хотите взять выходной сигнал флопа, который переключается в одной тактовой области, и сэмплировать его на другом флопе в быстрой тактовой области, тогда по определению ваше решение включает в себя соединение двух синхронных схем вместе.

Кроме того, я скажу, что «от медленного к быстрому» — слишком абстрактное определение, чтобы дать точный ответ, а также в вашем описании отсутствует множество переменных. Междоменное пересечение — очень обширная тема, и существует множество сценариев, каждый из которых можно обрабатывать и оптимизировать по-разному.

Теоретическая нижняя граница:

Минимальное время, необходимое для такой синхронизации, равно tSetup + tCQ + tHold одного флопа в области быстрых часов. Это связано с тем, что данные в медленной тактовой области должны оставаться стабильными на фронте тактовой частоты быстрого флопа, чтобы он мог правильно дискретизировать данные.

Если вы это гарантируете, метастабильности не будет, и можно сказать, что данные полностью синхронизированы.

Практическая лучшая нижняя граница:

Если исключить действительно сложные физические схемы, то минимальная задержка составляет один такт быстрого тактового домена, но ее можно реализовать только в определенных сценариях.

Например, если я перейду от медленной тактовой области X[МГц] к быстрой тактовой области n*X[МГц] (n — натуральное число), и обе тактовые частоты будут от одного и того же источника PLL, тогда вообще говоря, вы можете просто опробовать медленный сигнал, используя область быстрых часов, даже не давая ограничений по времени.

Это связано с тем, что инструмент синтеза считает это синхронным путем синхронизации и может гарантировать известное соотношение и фазу между фронтами двух тактовых импульсов. Таким образом, в этом сценарии синхронизатор представляет собой простой провал в области быстрых часов, нижняя (и верхняя) граница задержки составляет 1 цикл в области быстрых часов, и вам не нужен FIFO. Вам просто нужно знать, что результат этого флопа интересен один раз в каждые n тактов.

Практическая общая нижняя граница:

Я предполагаю самый общий случай:

- Два тактовых сигнала без какой-либо известной взаимосвязи, только то, что драйвер медленный, а приемник быстрый.

- Широкая шина, где необходимо сохранять соотношение между каждыми двумя битами.

- Ввод поступает каждый цикл

Ответ на этот сценарий скрыт в вашем вопросе: «Кажется очевидным, что данные необходимо будет зарегистрировать в обоих доменах, и потребуется некоторое время для междоменного пути и для разрешения метастабильности ».

Метастабильность не является обязательным явлением в каждом цикле. Если возникает метастабильность, то для разрешения метастабильности требуется (в общем случае цепочки провалов синхронизатора) еще один цикл. Следовательно, нижней границей процесса синхронизации является задержка схемы, когда нет метастабильности.

Для общего случая, который я описал выше, и опять же, исключая более сложные решения, зависящие от конкретного сценария, вам понадобится синхронизатор CDC FIFO.

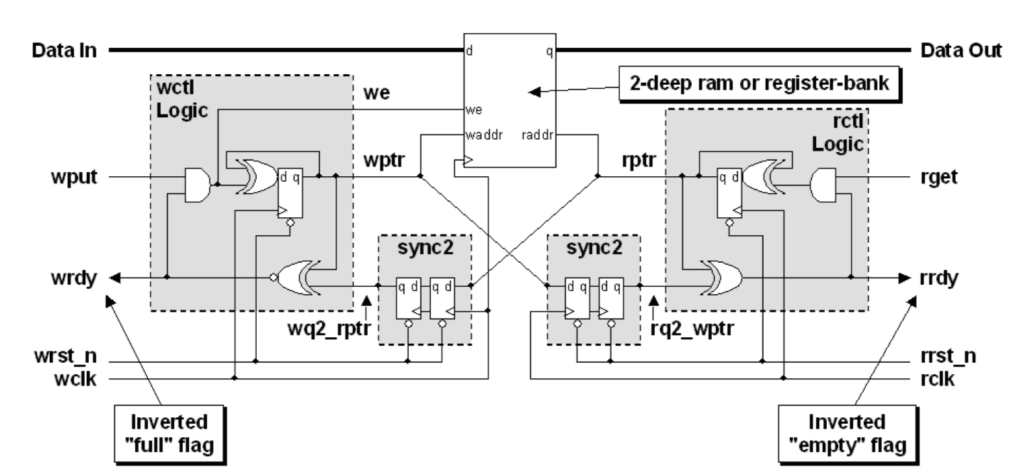

Нижняя граница задержки FIFO зависит от реализации внутренней цепочки синхронизаторов в FIFO. Это sync2 на рисунке ниже, взятом из превосходной статьи Клиффорда Э. Каммингса (ссылка ниже):

На этом рисунке цепь синхронизатора составляет 2 флопа. Таким образом, минимальная задержка этой схемы от wput до rrdy составляет 1 цикл медленного тактового сигнала (для выборки сигнала wput) и 2 цикла быстрого тактового сигнала. Если нам нужна верхняя граница, то нам нужно учитывать возможную метастабильность в цепи синхронизатора, поэтому мы получаем 1 цикл медленных тактовых импульсов и 3 цикла быстрых тактовых импульсов.

http://www.sunburst-design.com/papers/CummingsSNUG2008Boston_CDC.pdf