Systemverilog взаимодействует через иерархические границы

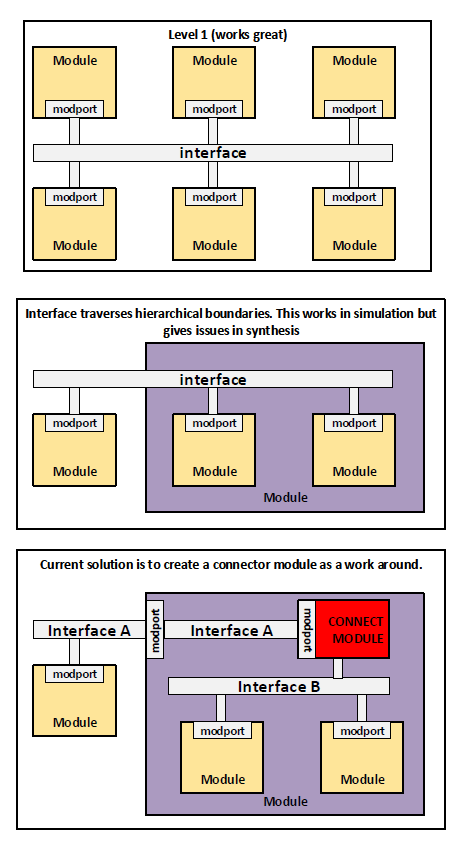

Я сталкивался с некоторыми внутренними проблемами при использовании интерфейсов systemverilog, когда интерфейс пересекает иерархические границы. Я попытался набросать ситуацию на прилагаемом чертеже.

На верхнем рисунке показан "обычный" метод использования интерфейсов. интерфейс и подключенный модуль создаются на одном уровне иерархии. Это работает для моделирования и бэк-энда.

Средняя картина показывает мою ситуацию. На верхнем уровне у меня есть модуль и интерфейс реализации. Интерфейс подключается к фиолетовому модулю, а затем подключается к 2 субмодулям. В симуляции это работает.

Затем инструмент синтеза жалуется, что интерфейс на фиолетовом уровне должен быть модпортом. Поэтому я добавил это. Однако инструмент синтеза интерпретирует провода как двунаправленные и добавляет логику для облегчения этого. В моем дизайне все провода однонаправлены.

Единственный обходной путь, который я смог найти, чтобы исправить эту проблему, изображен на нижнем рисунке. Я подключаю через модпорт оригинальный интерфейс (помеченный А). Затем я создаю новый интерфейс (помеченный B), у которого тот же родительский элемент, что и у интерфейса A. Оба интерфейса A и B подключены к соединительному модулю, который содержит множество операторов, таких как:

назначить interfaceB.rx1 = interfaceA.rx1;

назначить interfaceB.rx2 = interfaceA.rx2;

назначить interfaceA.statusX = interfaceB.statusX;

так далее

так что это просто "тупое" соединение интерфейса A и B.

Такой способ работы кажется очень неправильным, так как этот модуль подключения создает много накладных расходов. Есть ли хороший / более простой способ использования интерфейса через иерархические границы, который не только работает в симуляциях, но и работает для синтеза?

1 ответ

Иерархическая композиция, безусловно, является недостатком интерфейсов SystemVerilog.

Вы можете упростить свое решение, создав InterfaceB со списком портов и подключения к отдельным сигналам от InterfaceA порт. Это исключает подключение модуля.

interface InterfaceB( input rx1, rx2, output ...)'

modport .../ same as what you have

endinterface