Потоковые интерфейсы AXI в IP-генераторе системы Xilinx

У меня есть пример дизайна в системном генераторе для обработки изображений, который имеет одно входное изображение и одно выходное изображение. Я хотел бы отправлять данные через потоковый интерфейс AXI и экспортировать их в виде IP-ядра в IP-интегратор Vivado, а также разрабатывать дизайн с использованием DMA и программного обеспечения в SDK.

Во-первых, возможно ли иметь потоковый интерфейс AXI в моем дизайне? Если да, как я могу это реализовать? Кто-нибудь может мне помочь?

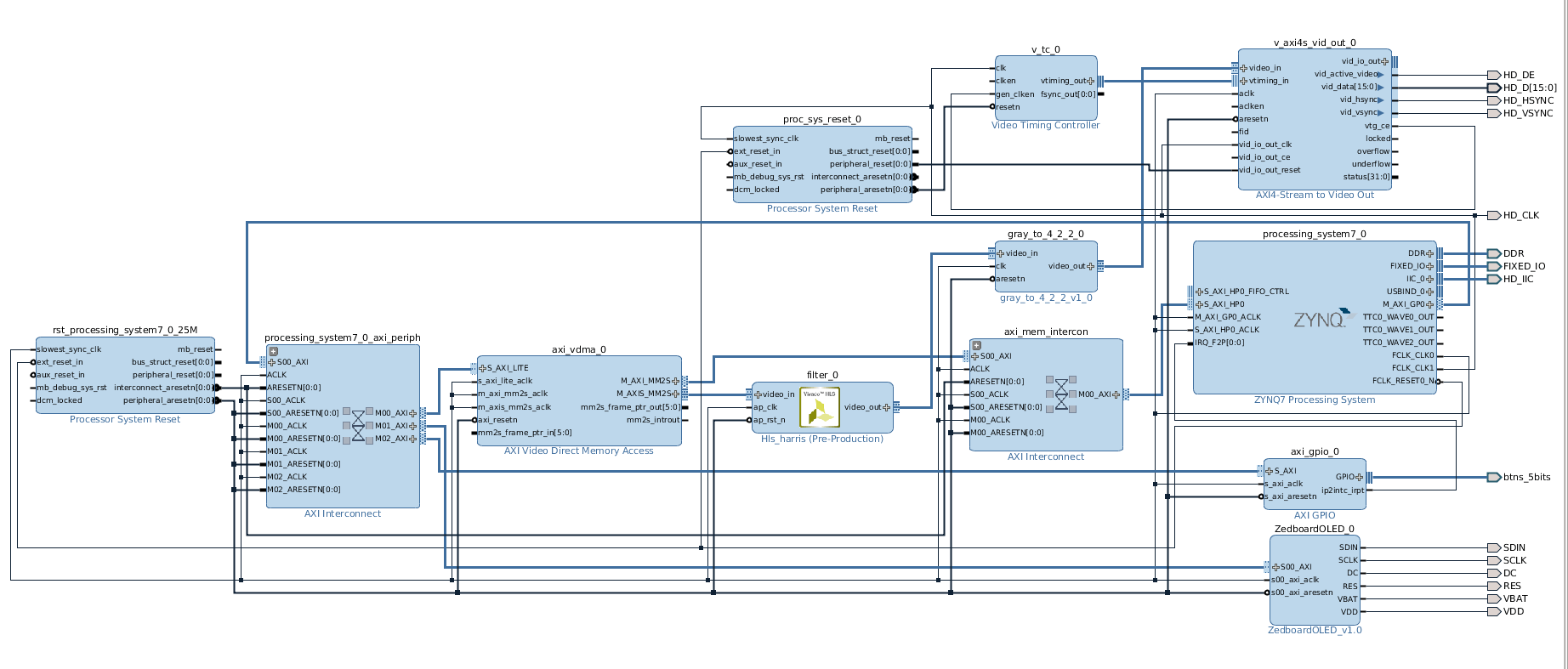

Заранее спасибо. (я приложил изображение примера здесь) Image_filter

3 ответа

В настоящее время я работаю над очень похожим проектом (хотя я не использую System Generator), так что держу пари, что могу дать вам несколько советов. Насколько я помню, SysGen может создать некоторый код VHDL или Verilog вашего дизайна. Так:

После того, как вы получите код HDL вашего дизайна, упакуйте его как новый IP в Vivado. Есть много учебников о том, как это сделать, это должно быть легко с небольшим поиском. Вы должны мудро выбирать интерфейсы, которые хотите реализовать. Вам определенно понадобится интерфейс AXI Stream Slave для приема входящих данных и интерфейс AXI Stream Master для передачи результатов.

После того, как вы упакуете свой IP, вы можете начать строить свою систему по блокам (есть также несколько хороших руководств по этому вопросу, см. Конец ответа). Вам нужно будет использовать AXI DMA IP (или Video DMA, в зависимости от ваших потребностей), и вам нужно будет правильно его настроить, например, выбрать режим регистрации или разброса, каналы и т. Д.

Будьте предельно осторожны, чтобы правильно генерировать правильные сигналы синхронизации AXI, так как они могут полностью разрушить ваш дизайн (и нервы). Это легко, но требует некоторого изучения документации AXI, предоставленной Xilinx (документы ARM слишком сложны для моего вкуса).

Наконец, вы обязательно найдете очень полезную информацию на следующих ресурсах:

Удачи!

PS: симуляторы твои друзья! Никогда не пытайтесь внедрить ваш недавно написанный код непосредственно в проект системы. Modelsim может сэкономить вам значительное время и усилия, которые в противном случае были бы потрачены на бессмысленную отладку.

Во-первых, возможно ли иметь потоковый интерфейс AXI в моем дизайне?

Да, это.

Если да, как я могу это реализовать? Кто-нибудь может мне помочь?

У меня есть похожий проект, разработанный в Vivado 2015.3: фильтр изображений (созданный с помощью "Синтез высокого уровня") и этот блок дизайна:

Код синтеза высокого уровня должен выглядеть следующим образом:

#include "top.h"

void hls_sobel(

hls::stream< ap_axiu<8,1,1,1> > &video_in,

hls::stream< ap_axiu<8,1,1,1> > &video_out

)

{

ap_uint<16> Image_w=IMAGE_W_MAX;

ap_uint<16> Image_h=IMAGE_H_MAX;

// Create AXI streaming interfaces for the core

#pragma HLS INTERFACE axis port=video_in bundle=video_in

#pragma HLS INTERFACE axis port=video_out bundle=video_out

// No control interface - auto-start as soon as there's an input frame

#pragma HLS INTERFACE ap_ctrl_none port=return // no handshakes

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_8UC1> mat_in(Image_h, Image_w);

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_8UC1> mat_out(Image_h, Image_w);

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_8UC1> inx(Image_h, Image_w);

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_8UC1> iny(Image_h, Image_w);

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_16SC1> sobelx(Image_h, Image_w);

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_16SC1> sobely(Image_h, Image_w);

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_16SC1> zerox(Image_h, Image_w);

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_16SC1> zeroy(Image_h, Image_w);

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_8UC1> absx(Image_h, Image_w);

hls::Mat<IMAGE_H_MAX, IMAGE_W_MAX, HLS_8UC1> absy(Image_h, Image_w);

#pragma HLS dataflow

// read input and convert from axi-stream to Mat

hls::AXIvideo2Mat(video_in, mat_in);

// calculate Sobel in X and Y directions

hls::Duplicate(mat_in, inx, iny);

hls::Sobel<1,0,3>(inx, sobelx);

hls::Sobel<0,1,3>(iny, sobely);

// calculate abs of said Sobel

hls::Zero(zerox);

hls::Zero(zeroy);

hls::AbsDiff(sobelx, zerox, absx);

hls::AbsDiff(sobely, zeroy, absy);

// add both abs

hls::AddWeighted(absx, 1, absy, 1, 0, mat_out);

// write output

hls::Mat2AXIvideo(mat_out, video_out);

}

Как вы можете заметить, DMA используется. Для приложения Video-Image я рекомендую использовать Video-DMA (VDMA) для отправки всей информации о пикселях через потоковый интерфейс. После этого в SDK легко управлять передачей, используя функцию из пакета поддержки платы (BSP).

Также можно заметить, что в приведенном выше коде явно указано hls::stream< ap_axiu<8,1,1,1> > &video_in,! Таким образом, я создаю потоковый интерфейс.

Здесь вы можете найти учебник о фильтре обработки изображений HLS. На последней странице есть полезные ссылки. Следуйте им, чтобы реализовать ту же систему примера.

Я надеюсь, что это может помочь

Если я правильно понимаю, вы хотите знать, как создать интерфейс AXI Stream внутри вашего системного генератора.

Да, это возможно. В вашем дизайне должно быть как минимум два входа с именами, например, image_tdata и image_tvalid (входной шлюз). Когда вы создаете IP-ядро, sysgen распознает его как AXI STREAM. Формат важен. Это должны быть «$customname_tdata» и «$customname_tvalid». Вы также можете добавить другие входные данные для добавления в AXI STREAM, такие как «$customname_tlast», «$customname_tready».