Моделирование структурной архитектуры в ACtive-HDL

Я написал два кода, которые успешно смоделированы в ISE Design Suit:

-- 2X1 Multiplexer

library IEEE;

use IEEE.STD_LOGIC_1164.all;

package mux2to1_pkg is

component mux2to1

port(d1,d0: in std_logic;

s: in std_logic;

f: out std_logic);

end component;

end mux2to1_pkg;

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity mux2to1 is

port(d1,d0: in std_logic;

s: in std_logic;

f: out std_logic);

end mux2to1;

architecture behavioral of mux2to1 is

begin

f <= (d0 and not s) or

(d1 and s);

end behavioral;

а также

-- 6X1 Multiplexer

library IEEE;

use IEEE.STD_LOGIC_1164.all;

package mux6to1_pkg is

component mux6to1

port(d: in std_logic_vector(5 downto 0);

s: in std_logic_vector(2 downto 0);

f: out std_logic);

end component;

end mux6to1_pkg;

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use WORK.mux2to1_pkg.all;

entity mux6to1 is

port(d: in std_logic_vector(5 downto 0);

s: in std_logic_vector(2 downto 0);

f: out std_logic);

end mux6to1;

architecture structural of mux6to1 is

signal m1,m2,m3,m4: std_logic;

begin

mux1: mux2to1 port map(d(5),d(4),s(0),m1);

mux2: mux2to1 port map(d(3),d(2),s(0),m2);

mux3: mux2to1 port map(d(1),d(0),s(0),m3);

mux4: mux2to1 port map(m2,m3,s(1),m4);

mux5: mux2to1 port map(m1,m4,s(2),f);

end structural;

Проблема в том, что когда я хочу смоделировать MUX6to1 в Active-HDL, выход не меняется вообще. В чем секрет этой программы? Ty.

1 ответ

Используя этот тестовый стенд:

library ieee;

use ieee.std_logic_1164.all;

entity mdl_tb is

end entity;

library ieee;

use ieee.numeric_std.all;

architecture sim of mdl_tb is

signal s_d : std_logic_vector(8 downto 0) := (others => '0');

signal f : std_logic;

begin

dut_e : entity work.mux6to1

port map(d => s_d(5 downto 0),

s => s_d(8 downto 6),

f => f);

process is

begin

wait for 1 ns;

s_d <= std_logic_vector(unsigned(s_d) + 1);

end process;

end architecture;

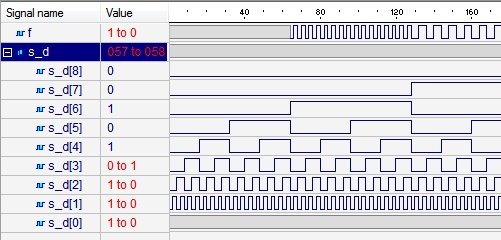

это показывает изменения как:

на основе этого сценария Active-HDL с двумя вышеупомянутыми файлами в mdl.vhd:

# Workspace "prod" create under current and open this workspace

workspace create prod

# Design "prod" create under current workspace

design create -a prod .

# Create to directory under workspace

cd $DSN/..

# Compile

acom ../mdl.vhd

acom ../mdl_tb.vhd

# Load module for simulation

asim work.mdl_tb

# Waveform add

add wave /mdl_tb/*

# Run

run 600 ns

Btw. Вы можете значительно сократить код, если пропустите объявления компонентов и связанные пакеты, используя такой код:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity mux2to1 is

port(d1,d0: in std_logic;

s: in std_logic;

f: out std_logic);

end mux2to1;

architecture behavioral of mux2to1 is

begin

f <= d0 when (s = '0') else d1;

end behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity mux6to1 is

port(d: in std_logic_vector(5 downto 0);

s: in std_logic_vector(2 downto 0);

f: out std_logic);

end mux6to1;

architecture structural of mux6to1 is

signal m1,m2,m3,m4: std_logic;

begin

mux1: entity work.mux2to1 port map(d(5),d(4),s(0),m1);

mux2: entity work.mux2to1 port map(d(3),d(2),s(0),m2);

mux3: entity work.mux2to1 port map(d(1),d(0),s(0),m3);

mux4: entity work.mux2to1 port map(m2,m3,s(1),m4);

mux5: entity work.mux2to1 port map(m1,m4,s(2),f);

end structural;