VHDL Tristate выход в решетке алмаза

Я пытаюсь написать модуль для чтения / записи в интерфейс (CY7C1011CV33 -10ns), но мне трудно вывести что-то на входной порт. Мне удалось заставить вещи работать достаточно близко к тому, что я хочу, но теперь у меня другая проблема. Когда я добавляю этот модуль в свой дизайн, я могу синтезировать, но когда я пытаюсь создать карту, я получаю следующую ошибку:

ВНИМАНИЕ - Регистр MEMORY/Opin_11__I_0_i2 имеет синхронизирующий сигнал, связанный с GND. ПРЕДУПРЕЖДЕНИЕ - Регистр MEMORY/Opin_11__I_0_i3 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - Регистр MEMORY/Opin_11__I_0_i4 имеет синхронизирующий сигнал, связанный с GND. ПРЕДУПРЕЖДЕНИЕ - Регистр MEMORY/Opin_11__I_0_i5 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - Регистр MEMORY/Opin_11__I_0_i6 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - Регистр MEMORY/Opin_11__I_0_i7 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - Регистр MEMORY/Opin_11__I_0_i8 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - Регистр MEMORY/Opin_11__I_0_i9 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - Регистр MEMORY/Opin_11__I_0_i10 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - Регистр MEMORY/Opin_11__I_0_i11 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - Регистр MEMORY/Opin_11__I_0_i12 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - Регистр MEMORY / Opin_11__I_0_i1 имеет синхронизирующий сигнал, связанный с GND. ВНИМАНИЕ - EHXPLLJ 'OSCmain/PLLInst_0' не может получить FREQUENCY_PIN_CLKOP=260.000, когда FREQUENCY_PIN_CLKI=133.000, CLKI_DIV=5, CLKFB_DIV=13, CLKOP_DIV=2. ОШИБКА - В L6MUX21 MUX/i672/GATE отсутствует ввод данных. Проверьте на висячие сети или логику. ИНФОРМАЦИЯ - Обнаружены ошибки в дизайне пользователя. Выходные файлы не записаны. Проверьте отчет карты для более подробной информации.

эта часть работала раньше, поэтому, когда я найду проблему, я обновлю здесь

обновление к коду и тестбенч добавил обновление 2: добавлена более новая версия кода, почти работает

новый код: это делает то, что я хочу, более или менее, мне просто нужно настроить время, но он синтезирует.

---------------------------------------------------

-- Ainda sendo escrito

-- Vai comunicar com o SRAM CY7C1011CV33 -10ns

---------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity SRAM is

generic(n: natural :=12 );

Port (

-- FPGA INTERNAL ----

clk : in STD_LOGIC; -- internal clock

send : in STD_LOGIC; -- low to send data

get : in STD_LOGIC; -- low to get data

Ipin : in STD_LOGIC_VECTOR (11 downto 0); -- data to send to sram

Opin : out STD_LOGIC_VECTOR (11 downto 0); -- data to send to fpga

add : in STD_LOGIC_VECTOR (16 downto 0); -- sram address input

drdy : out std_logic; -- data ready

---------------------------------------------

-- To sram ----------------------------------

---------------------------------------------

Address : out STD_LOGIC_VECTOR (16 downto 0);

Data : inout STD_LOGIC_VECTOR (11 downto 0);

CE : out STD_LOGIC;

WE : out STD_LOGIC;

OE : out STD_LOGIC;

BHE : out STD_LOGIC

);

end SRAM;

architecture Behavioral of SRAM is

signal clk_div : STD_LOGIC_VECTOR (1 downto 0) := B"00";

signal clk_PH : STD_LOGIC_VECTOR (1 downto 0) := B"00";

signal Zero : STD_LOGIC_VECTOR (n-1 downto 0) := B"000000000000";

-- for inout port

signal tmpdata : STD_LOGIC_VECTOR(11 downto 0);

signal TMPCE : STD_LOGIC := '1';

signal TMPWE : STD_LOGIC := '1';

signal TMPOE : STD_LOGIC := '1';

signal TMPBHE : STD_LOGIC := '1';

signal TMPDRDY : STD_LOGIC := '1';

begin

-- clock divider

process (clk)

begin

if (rising_edge(clk) and (send ='0' or get = '0')) then

clk_div <= clk_div + '1';

end if;

end process;

-- clock divider phase 90

process (clk)

begin

if (falling_edge(clk) and (send ='0' or get = '0')) then

clk_ph <= clk_ph + '1';

end if;

end process;

process(clk_div, clk_ph, clk)

begin

-- WRITE TO SRAM

if (send = '0') then

Address <= add;

tmpdata <= Zero;

TMPCE <= '0';

TMPWE <= '0';

TMPOE <= '1';

TMPBHE <= '0';

TMPdrdy <= '1';

TMPCE <= '1';

TMPWE <= '1';

TMPOE <= '1';

TMPBHE <= '1';

TMPdrdy <= '1';

case clk_div is

when b"00" =>

TMPCE <= '0';

TMPWE <= '0';

TMPOE <= '1';

TMPBHE <= '0';

TMPdrdy <= '1';

when b"01" =>

TMPCE <= '0';

TMPWE <= '0';

TMPOE <= '1';

TMPBHE <= '0';

TMPdrdy <= '1';

when others =>

TMPCE <= '1';

TMPWE <= '1';

TMPOE <= '1';

TMPBHE <= '1';

TMPdrdy <= '1';

end case;

case clk_ph is

--when b"00" =>

--tmpdata <= Ipin;

when b"01" =>

tmpdata <= Ipin;

when b"10" =>

tmpdata <= Ipin;

when others =>

tmpdata <= Zero;

end case;

end if;

-- READ FROM SRAM

if (send = '1' and get ='0') then

Address <= add;

TMPCE <= '0';

TMPOE <= '0';

TMPBHE <= '0';

TMPWE <= '1';

TMPDRDY <= '1';

case clk_div is

when b"01" =>

Opin <= data;

when b"10" =>

Opin <= data;

TMPDRDY <= '0';

when others =>

TMPCE <= '1';

TMPWE <= '1';

TMPOE <= '1';

TMPBHE <= '1';

end case;

end if;

end process;

Data <= tmpdata when send = '0' else (others => 'Z');

CE <= TMPCE;

WE <= TMPWE;

OE <= TMPOE;

BHE <= TMPBHE;

drdy <= TMPDRDY;

end Behavioral;-- VHDL Test Bench Created from source file SRAM.vhd -- Wed May 30 21:37:25 2018

--

-- Notes:

-- 1) This testbench template has been automatically generated using types

-- std_logic and std_logic_vector for the ports of the unit under test.

-- Lattice recommends that these types always be used for the top-level

-- I/O of a design in order to guarantee that the testbench will bind

-- correctly to the timing (post-route) simulation model.

-- 2) To use this template as your testbench, change the filename to any

-- name of your choice with the extension .vhd, and use the "source->import"

-- menu in the ispLEVER Project Navigator to import the testbench.

-- Then edit the user defined section below, adding code to generate the

-- stimulus for your design.

-- 3) VHDL simulations will produce errors if there are Lattice FPGA library

-- elements in your design that require the instantiation of GSR, PUR, and

-- TSALL and they are not present in the testbench. For more information see

-- the How To section of online help.

--

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY testbench IS

END testbench;

ARCHITECTURE behavior OF testbench IS

COMPONENT SRAM

PORT(

clk : IN std_logic;

send : IN std_logic;

get : IN std_logic;

Ipin : IN std_logic_vector(11 downto 0);

add : IN std_logic_vector(16 downto 0);

Data : INOUT std_logic_vector(11 downto 0);

Opin : OUT std_logic_vector(11 downto 0);

drdy : OUT std_logic;

Address : OUT std_logic_vector(16 downto 0);

CE : OUT std_logic;

WE : OUT std_logic;

OE : OUT std_logic;

BHE : OUT std_logic

);

END COMPONENT;

SIGNAL clk : std_logic;

SIGNAL send : std_logic;

SIGNAL get : std_logic;

SIGNAL Ipin : std_logic_vector(11 downto 0);

SIGNAL Opin : std_logic_vector(11 downto 0);

SIGNAL add : std_logic_vector(16 downto 0);

SIGNAL drdy : std_logic;

SIGNAL Address : std_logic_vector(16 downto 0);

SIGNAL Data : std_logic_vector(11 downto 0);

SIGNAL CE : std_logic;

SIGNAL WE : std_logic;

SIGNAL OE : std_logic;

SIGNAL BHE : std_logic;

constant delay : time := 10 ns;

BEGIN

-- Please check and add your generic clause manually

uut: SRAM PORT MAP(

clk => clk,

send => send,

get => get,

Ipin => Ipin,

Opin => Opin,

add => add,

drdy => drdy,

Address => Address,

Data => Data,

CE => CE,

WE => WE,

OE => OE,

BHE => BHE

);

send <= '0';

get <= '1';

Ipin <= B"000011110000";

add <= B"00000000000000001";

-- *** Test Bench - User Defined Section ***

tb : PROCESS

BEGIN

clk <= '0';

wait for delay;

clk <= '1';

wait for delay;

clk <= '0';

wait for delay;

clk <= '1';

wait for delay;

clk <= '0';

wait for delay;

clk <= '1';

wait for delay;

clk <= '0';

wait for delay;

clk <= '1';

END PROCESS;

-- *** End Test Bench - User Defined Section ***

END;

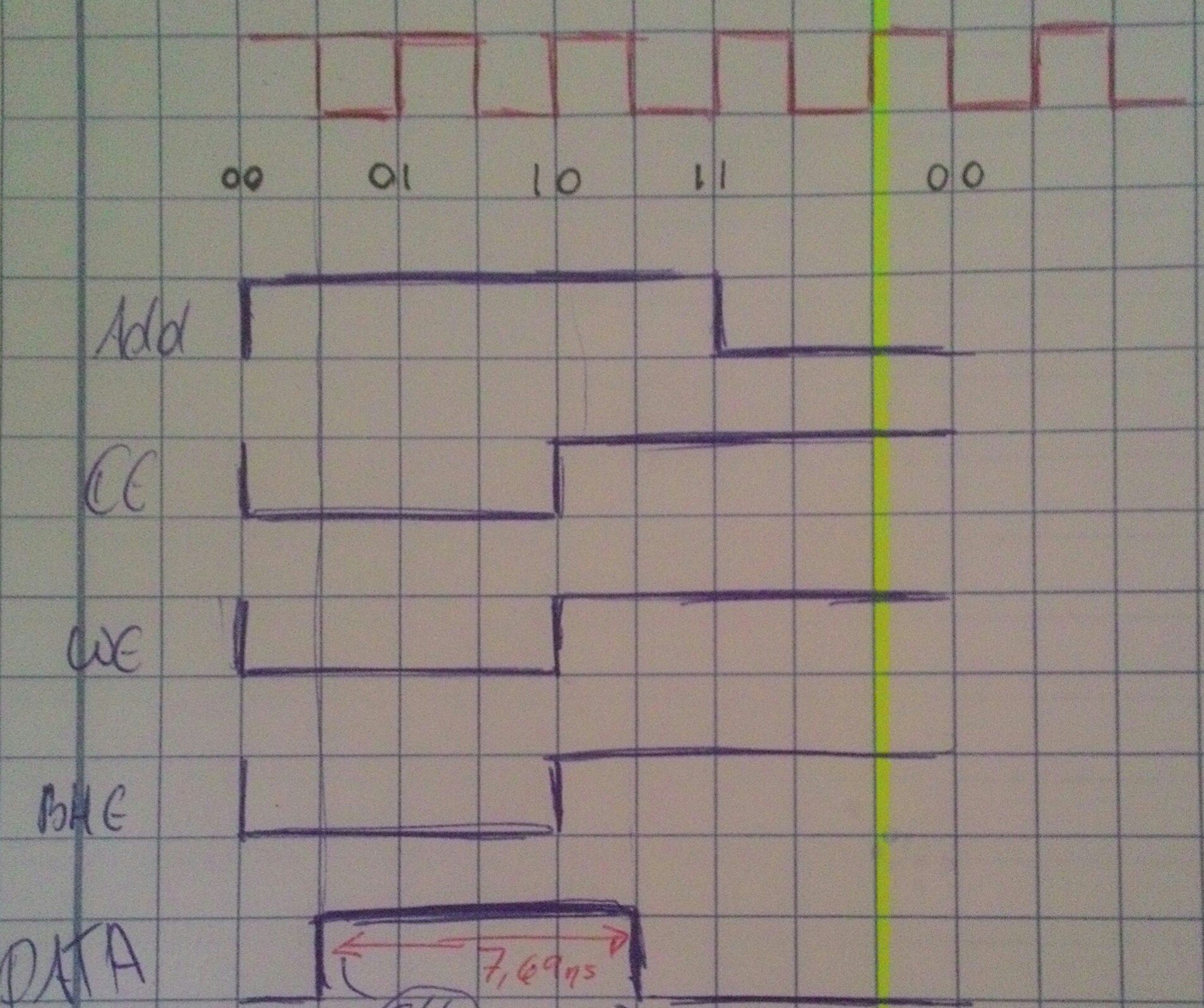

Я все еще учусь работать с VHDL и fpga, поэтому я представляю, что во всем моем мыслительном процессе довольно много ошибок, хотя этот код. вот быстрый рисунок того, что я пытаюсь произвести (когда что-то идет высоко, это просто означает, что что-то передается, и добавить, что в конце не нужно идти вниз):