PHY Marvell 88E1518

Я построил специальную плату с cyclone10GX и phy marvell 88E1518 в режиме RGMII. У меня было аналогичное оборудование, работающее нормально, используя cycloneIII и marvell 88E1111 в режиме RGMII.

Не удалось запустить тот же проект, состоящий из полного аппаратного стека UDP/IP на 1 Гб.

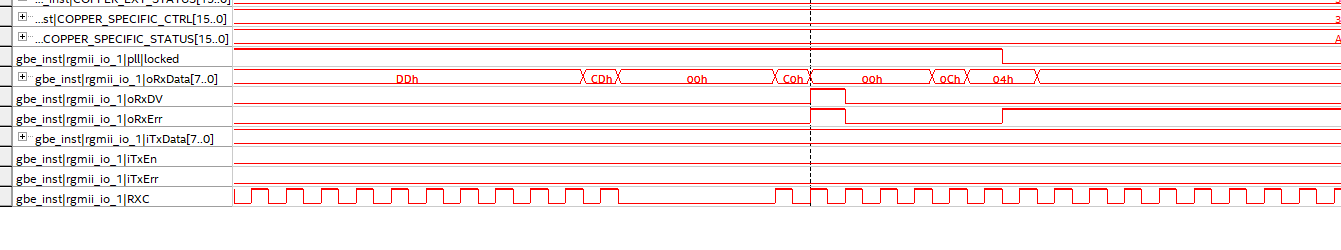

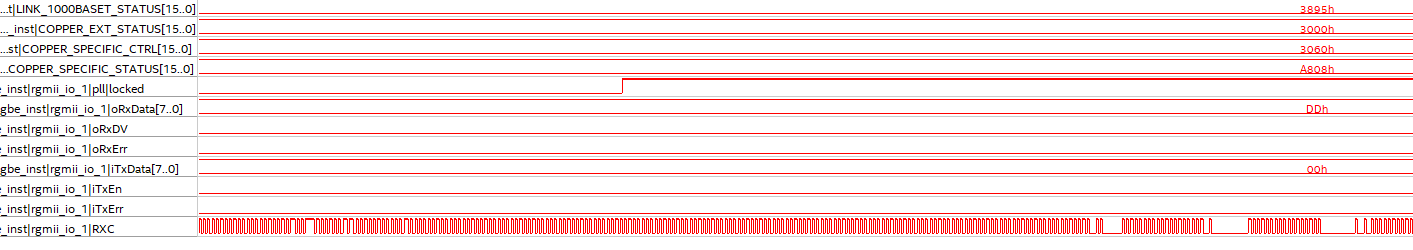

Я включил зонд signaltap после DDIO на пути приема и RX_CLK файла phy. Эти часы питают IOPLL, управляя всем внутри FPGA.

Удивительно, но входная тактовая частота RX_CLK снижается на некоторый цикл и разблокирует ФАПЧ.

Я постоянно проверяю некоторые регистры MDIO, чтобы понять, что происходит. Регистр 10 страница 0 сообщает об ошибках IDLE, хотя я не делаю ничего особенного. Из того, что я знаю о 802.3, IDLE - это межпакетный промежуток, необходимый между двумя пакетами. На странице 41 таблицы данных говорится:

В режиме 1000BASE-T поток ожидания приема анализируется, чтобы можно было учесть начальное значение скремблера, перекос между 4 парами, порядок перестановки пар и полярность пар. После калибровки символы 4D PAM 5 преобразуются в 9-битные символы, которые затем дескремблируются в 8-битовые значения данных. Если дескремблер теряет блокировку по какой-либо причине, связь отключается, и калибровка перезапускается после завершения автосогласования.

Я не знаю, где искать ошибки. Если кто-нибудь знает, что может случиться, я был бы очень признателен за помощь.

Джон