Двунаправленный буфер с тремя состояниями

Я работаю над проектом, в котором мне нужен двунаправленный буфер с тремя состояниями. Я разработал VHDL-код, основанный на моих поисках в этом сообществе и на некоторых других сайтах. Но это не работает так, как должно. Ниже приведен код VHDL.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity Inter_Con_Mod is

generic(WL: integer := 8);

port(In1: in signed(WL-1 downto 0);

RW: in std_logic;

Data_IO1: inout signed(WL-1 downto 0);

Out1: out signed(WL-1 downto 0));

end Inter_Con_Mod;

architecture Behav of Inter_Con_Mod is

begin

Data_IO1 <= In1 when RW = '1' else

(others => 'Z');

Out1 <= Data_IO1;

end Behav;

Это код тестового стенда:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY InterCon_test IS

END InterCon_test;

ARCHITECTURE behavior OF InterCon_test IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT Inter_Con_Mod

PORT(

In1 : IN signed(7 downto 0);

RW : IN std_logic;

Data_IO1 : INOUT signed(7 downto 0);

Out1 : OUT signed(7 downto 0)

);

END COMPONENT;

--Inputs

signal In1 : signed(7 downto 0) := (others => '0');

signal RW : std_logic := '0';

--BiDirs

signal Data_IO1 : signed(7 downto 0);

--Outputs

signal Out1 : signed(7 downto 0);

-- No clocks detected in port list. Replace <clock> below with

-- appropriate port name

--constant <clock>_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: Inter_Con_Mod PORT MAP (

In1 => In1,

RW => RW,

Data_IO1 => Data_IO1,

Out1 => Out1

);

-- Clock process definitions

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 5 ns;

In1 <= "01111111";

wait for 5 ns;

RW <= '1';

wait for 5 ns;

RW <= '0';

wait for 20 ns;

Data_IO1 <= "00101010";

wait;

end process;

END;

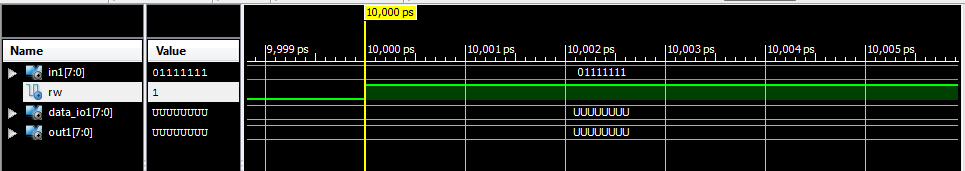

Но посмотрите, что происходит в результате симуляции. Результат:

Я не понимаю, почему он игнорирует стимуляцию тестового стенда, которую я предоставил перед установкой RW в 0.

Заранее спасибо.

1 ответ

Благодаря @user1155120 проблема была решена. Я изменил весь код на то, что будет ниже.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity Inter_Con_Mod is

generic(WL: integer := 8);

port(PortL,PortR: inout signed(WL-1 downto 0);

RW: in std_logic);

end Inter_Con_Mod;

architecture Behav of Inter_Con_Mod is

begin

PortR <= PortL when RW = '0' else

(others => 'Z');

PortL <= PortR when RW = '1' else

(others => 'Z');

end Behav;

Таким образом, у меня есть 2 входных порта и один входной порт выбора. Проблема была не в коде модуля. Это было в стенде. Я должен был управлять входным портом, который мне нужен, чтобы действовать как выход, чтобы не иметь помех данных на линии. Ниже приведен код Testbench:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY Test IS

END Test;

ARCHITECTURE behavior OF Test IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT Inter_Con_Mod

PORT(

PortL : INOUT signed(7 downto 0);

PortR : INOUT signed(7 downto 0);

RW : IN std_logic

);

END COMPONENT;

--Inputs

signal RW : std_logic := '0';

--BiDirs

signal PortL : signed(7 downto 0);

signal PortR : signed(7 downto 0);

-- No clocks detected in port list. Replace <clock> below with

-- appropriate port name

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: Inter_Con_Mod PORT MAP (

PortL => PortL,

PortR => PortR,

RW => RW

);

-- Stimulus process

stim_proc: process

begin

PortL <= "01111111";

PortR <= (others => 'Z');

wait for 5 ns;

RW <= '1';

wait for 5 ns;

PortR <= "01111100";

PortL <= (others => 'Z');

wait for 20 ns;

wait;

wait;

end process;

END;

Я надеюсь, что это может помочь тем, кто плохо знаком с оборудованием, как я.