Port_ID изменяется случайным образом, а outport иногда дает входные данные.

Я пытаюсь сделать сумматор с picoblaze, но я столкнулся с некоторыми проблемами.

Вот мой код для рисования:

LOAD s1,00

LOAD s0,00

start:

INPUT s0,00

ADD s1,s0

OUTPUT s1,01

JUMP start

Затем я поместил этот код в verilog с помощью kcpsm3 и написал верхний модуль и некоторый код:

module top_module(

input clock,

input reset

);

integer i;

wire [7:0] out_port;

wire [9:0] address;

wire [17:0] instruction;

wire [7:0] port_id;

wire write_strobe;

wire read_strobe;

reg [7:0] in_port;

wire interrupt;

wire interrupt_ack;

reg [7:0] counter ;

pico2 picoblaze2_asm (

.address(address),

.instruction(instruction),

.proc_reset(proc_reset),

.clk(clock)

);

kcpsm3 picoblaze2 (

.address(address),

.instruction(instruction),

.port_id(port_id),

.write_strobe(write_strobe),

.out_port(out_port),

.read_strobe(read_strobe),

.in_port(in_port),

.interrupt(interrupt),

.interrupt_ack(interrupt_ack),

.reset(reset),

.clk(clock)

);

initial begin

counter = 0;

i = 0;

end

always @ (posedge clock)

begin

counter = counter+1;

if(counter == 8)

begin

i = i+1;

in_port = i;

counter = 0;

if(i == 10)

begin

i = 0;

end

end

end

endmodule

Вот наш тестовый стенд:

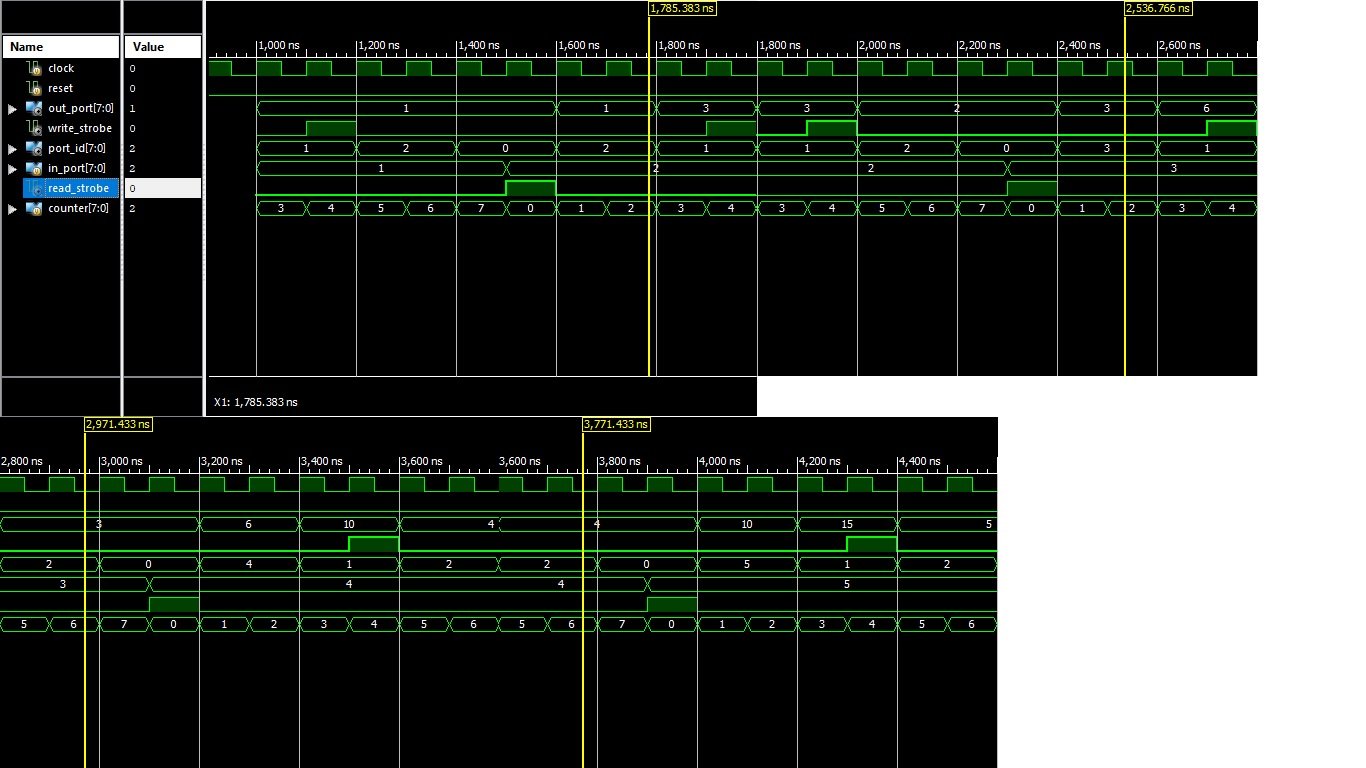

port_id занимает 0,1,2, а некоторые входные данные, такие как 3,4,5, но мы хотим взять 0 и 1 из-за кода сборки picoblaze. Во-вторых,out_port принимает добавленную стоимость (inport = 1,2 outport = 1+2 =3) и некоторые входные данные 3,4,5, которые мы хотим получить только добавленную стоимость без входной стоимости.

Подобно:

*inport 1 2 3 4 5 6

*outport 1 3 6 10 15 21

*port id 0 1 0 1 0 1 0 1 0 1.....