Ошибка в моем коде VHDL, но я не могу понять, почему

Я написал VHDL-код для показанной диаграммы состояния (не могу опубликовать изображение, потому что я новый пользователь). Однако, когда я компилирую его, он говорит, что есть ошибки: в строке 16: process(clk) - синтаксическая ошибка, обнаруженная во время разбора строки 21: else - синтаксическая ошибка, обнаруженная во время разбора строки 23: конец, если; - синтаксическая ошибка, обнаруженная во время синтаксического анализа.

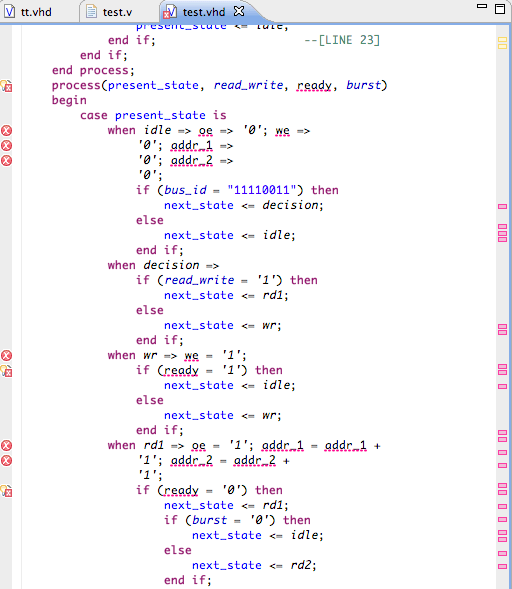

Это мой код:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.ALL;

entity memory_controller is

port(clk: in std_logic;

reset: in std_logic;

bus_id: in std_logic_vector(7 downto 0);

read_write, burst: in std_logic;

oe, we, addr_1, addr_2: out std_logic

);

end memory_controller;

architecture behavioral of memory_controller is

type statetype is (idle, decision, wr, rd1, rd2, rd3, rd4);

signal present_state, next_state : statetype;

process(clk) [LINE 16]

begin

if (rising_edge(clk)) then

if (reset ='0') then

present_state <= next_state;

else [LINE 21]

present_state <= idle;

end if; [LINE 23]

end if;

end process;

process(present_state, read_write, ready, burst)

begin

case present_state is

when idle =>

oe => '0'; we=> '0'; addr_1=> '0'; addr_2=> '0';

if(bus_id = "11110011") then

next_state <= decision;

else

next_state <= idle;

end if;

when decision =>

if (read_write = '1')

then next_state <= rd1;

else next_state <= wr;

end if;

when wr =>

we = '1';

if (ready = '1')

then next_state <= idle;

else

next_state <= wr;

end if;

when rd1 =>

oe = '1';

addr_1 = addr_1 + '1';

addr_2 = addr_2 + '1';

if(ready = '0') then

next_state <= rd1;

if(burst = '0') then

next_state <= idle;

else next_state <= rd2;

end if;

when rd2 =>

oe = '1';

addr_1 = addr_1 + '1';

addr_2 = addr_2 + '1';

if(ready = '1') then

next_state => rd3;

else

next_state => rd2;

end if;

when rd3 =>

oe = '1';

addr_1 = addr_1 + '1';

addr_2 = addr_2 + '1';

if(ready = '1') then

next_state => rd4;

else

next_state => rd3;

when rd4 =>

oe = '1';

addr_1 = addr_1 + '1';

addr_2 = addr_2 + '1';

if(ready = '1')

then next_state => idle;

else next_state => rd4;

end if;

end case;

end process;

end behavioral;

Синтаксис совершенно правильный, я не понимаю, почему это ошибка. Что может быть не так?

Кроме того, я хочу использовать операторы assert для случаев, когда ready =0, burst =0 и ready = 0 и burst = 1, но я не настолько уверен, как реализовать их в основном коде.

Я выделил строки 16, 21 и 23.

Любая помощь будет отличной.

2 ответа

Форма модуля VHDL обычно:

entity MODULENAME is

<Port description>

end MODULENAME;

architecture behavioral of MODULENAME is

<signal declarations and similar>

begin

<synchronous and combinatorial logic statements>

end architecture behavioral;

Чего вам не хватает, так это begin после вашего сигнала объявлений. То есть изменение

architecture behavioral of memory_controller is

type statetype is (idle, decision, wr, rd1, rd2, rd3, rd4);

signal present_state, next_state : statetype;

process(clk) [LINE 16]

begin

if (rising_edge(clk)) then

Для того, чтобы:

architecture behavioral of memory_controller is

type statetype is (idle, decision, wr, rd1, rd2, rd3, rd4);

signal present_state, next_state : statetype;

begin

process(clk) [LINE 16]

begin

if (rising_edge(clk)) then

Как указывает Sonicwave, вам не хватает begin Ключевое слово перед вашим первым заявлением.

Есть еще несколько синтаксических ошибок. При назначении сигналов используется стрелка влево:

- не

oe => '0';ноoe <= '0'; - не

we = '1';ноwe <= '1';

Если вы используете редактор с прямой обратной связью компилятора, вы сэкономите много времени.