Функция с небезразличными входами

Как я могу реализовать функцию VHDL, у которой есть входы "все равно" и в которой "все равно" должны быть представлены напрямую?

Упражнение 4.8-2a свободного диапазона VHDL просит меня:

... написать модели VHDL, которые реализуют эти функции, используя... выбранное назначение сигнала.

а) F (A, B, C, D) = A'CD' + B'C + BCD'

Этот код работает:

library ieee;

use ieee.std_logic_1164.all;

entity funca_selected is

port (

a: in std_ulogic;

b: in std_ulogic;

c: in std_ulogic;

d: in std_ulogic;

x: out std_ulogic);

end entity;

architecture rtl of funca_selected is

signal s: std_ulogic_vector(3 downto 0);

begin

s <= a & b & c & d;

with s select x <=

'1' when "0010" | "0110" | "0011" | "1010" | "1011" | "1110",

'0' when others;

end architecture;

Это, однако, плохое представление определения функции. Я хочу закодировать его, используя входные данные "пофиг", чтобы код более точно соответствовал определению. Это было бы меньше работы, и легче получить права. Я попробовал это:

with s select x <=

'1' when "0-10" | "-01-" | "-110",

'0' when others;

Это не работает: когда мой испытательный стенд выполняет эту функцию, результат всегда равен 0.

Я использую GHDL версии 0.29+gcc4.3.i386.

Как функция VHDL может представлять входные данные "все равно"?

4 ответа

С пометкой над панелью (как A () функция из упражнения 4.8-2a:

F (A, B, C, D) = A̅CD̅ + B̅C + BCD̅

GHDL поддерживает только максимум VHDL-2000 (в соответствии с функциями GHDL), поэтому ни одна из операций сравнения VHDL-2008 с проверкой "пофиг" ('-') недоступна. Альтернативным выражением для GHDL является выражение:

x <= ((not a) and c and (not d)) or

((not b) and c) or

(b and c and (not d));

Однако, если VHDL-2008 доступен в инструментах, то оператор?=, Который проверяет, не заботится, может использоваться как:

x <= (s ?= "0-10") or (s ?= "-01-") or (s ?= "-110");

Обратите внимание, что это выражение также применяет неявное логическое значение VHDL-2008 к преобразованию std_logic.

Или случай?, Который также проверяет на безразличие, может использоваться как:

process (s) is

begin

case? s is

when "0010" | "0110" | "0011" | "1010" | "1011" | "1110" => x <= '1';

when others => x <= '0';

end case?;

end process;

Нет с? оператор в VHDL-2008 для одновременного назначения по типу.

Дополнительную информацию о функциях VHDL-2008 можно найти здесь: VHDL-2008: Почему это важно.

Я попробовал обе версии логики в Xilinx ISE 14.6, и обе версии работают, но есть некоторые предостережения. Прежде всего, когда я сравниваю RTL Schematic версии "пофиг" с явной версией, версия "пофиг" намного проще и более оптимизирована. Версия "пофиг" имеет четыре логических элемента, и максимальные входные строки на каждый элемент составляют три строки. Явная версия имеет семь логических элементов, и максимальные входные строки на один элемент составляют шесть строк.

Когда я тестирую стенд для двух версий, у меня есть четыре различных варианта симуляции: Поведенческий, Пост-Перевод, Пост-Карта и Пост-Маршрут. В поведенческой модели вывод версии "пофиг" представляет собой плоскую линию, как вы заявили, и кажется, что версия "пофиг" не работает, однако, во всех трех других вариантах моделирования обе версии работают отлично и выводят идентичен Таким образом, похоже, что поведенческая модель не знает, как обрабатывать "не заботящиеся" части кода VHDL, но код является синтезируемым, и использование "не заботиться" в коде VHDL очень ценно.

Да, на ghdl можно рассчитывать только на соответствие стандарту IEEE Std 1076-1993, и в этом есть одна или две дыры.

Функция может быть проще, когда мы понимаем, что первый член (A (CD̅) не нужен, и где результат зависит от него. Первый термин продукта никогда не раскрывается в выходных данных.

Независимо от цели оценки выбранного назначения сигнала является выражением. Вы можете использовать выражение из оператора одновременного назначения сигналов MortenZdk:

library ieee;

use ieee.std_logic_1164.all;

entity f_test is

end;

architecture test of f_test is

subtype vector is std_logic_vector (3 downto 0);

type vectorstream is array (0 to 15) of vector;

constant stimulous: vectorstream :=(

x"0",x"1",x"2",x"3",x"4",X"5",x"6",x"7",

x"8",x"9",x"A",x"B",x"C",x"D",x"E",X"F"

);

signal index: integer range 0 to 15;

signal a,b,c,d: std_logic;

signal x: std_logic;

begin

Test_Vectors:

process

variable TV: std_logic_vector(3 downto 0);

begin

-- first term is valid

for i in vectorstream'range loop

index <= (i); -- make vector index visible in waveform

TV := vector(stimulous(i));

a <= TV(3); b <= TV(2); c <= TV(1); d <= TV(0);

wait for 10 ns;

end loop;

wait; -- ends simulation

end process;

EVALUATE: -- "the code more closely matches the definition"

with TO_X01(

( not a and c and not d) or -- b is don't care

( not b and c ) or -- a, d are don't care

( b and c and not d) -- a is don't care

) select x <= '1' when '1',

'0' when '0',

'X' when 'X'; -- equivalent of 'else 'X' in

-- concurrent signal assignment

end;

TO_X01 называется средством снятия прочности, относится к пакету std_logic_1164 и оценивается как 'X', '0' или '1'.

Выбранное назначение сигнала имеет условный эквивалент назначения сигнала, и оба могут быть выражены как процессы, то есть как они моделируются.

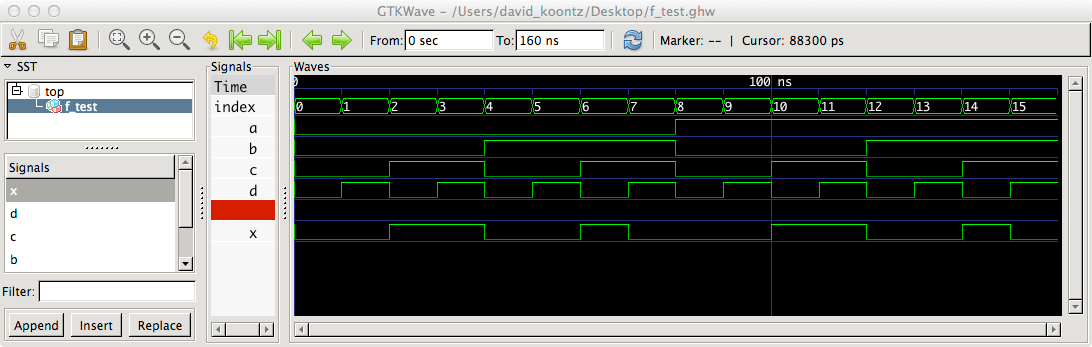

ghdl -a f_test.vhdl

ghdl -r f_test --wave=f_test.ghw

open f_test.ghw

Вы можете добавить кстилу, позволяющую демонстрировать распространение значений других элементов, как указано в stdlogic_table для "и" и для "или" в пакете std_Logic_1164, сопоставленного с типом X01, чтобы уменьшить количество вариантов выбора в выбранном операторе назначения сигнала.

Также обратите внимание на select x <= '1', когда '1', первое '1' относится к значению std_logic, а второе '1' относится к значению типа X01.

Вы можете закомментировать первую строку терминов продукта для A̅CD̅, чтобы продемонстрировать, что она не влияет на результат x.

Сравнения в VHDL являются очень чистым совпадением элементов за элементом. Это был один из недостатков VHDL, который получил расширение, чтобы исправить это в VHDL-2008, с case? заявление и =? оператор

http://www.doulos.com/knowhow/vhdl_designers_guide/vhdl_2008/vhdl_200x_small/

К сожалению, VHDL-2008 не поддерживается в GHDL, поэтому вам придется использовать std_match функция, которая, я думаю, также исключает использование with..select,