Как поместить список ячеек в подмодуль в yosys

Я пытаюсь написать процедуру для помещения каждого Сильно Связанного Компонента данной схемы в отдельный субмодуль.

Итак, я попытался добавить функцию для передачи SCC в Yosys, чтобы добавить каждый SCC в подмодуль. Функция:

void putSelectionIntoParition (RTLIL::Design *design,

std::vector<pair<std::string,RTLIL::Selection>>& SelectionVector)

{

int p_count = 0;

for (std::vector<pair<std::string,RTLIL::Selection>>::iterator it = SelectionVector.begin();

it != SelectionVector.end(); ++it)

{

design->selection_stack[0] = it->second;

design->selection_stack[0].optimize(design);

std::string command = "submod -name ";

command.append(it->first);

Pass::call_on_selection(design, it->second, command);

++p_count;

}

}

Тем не менее, мой код не работает должным образом. Я предполагаю, что проблема заключается в процессе выбора, который я использую. Мне было интересно, есть ли какая-либо утилита /API внутри источника yosys, которая принимает вектор ячеек (а также подмодуль имени) и помещает их в подмодуль.

1 ответ

Следующее должно работать просто отлично:

void putSelectionIntoParition(RTLIL::Design *design,

std::vector<pair<std::string, RTLIL::Selection>> &SelectionVector)

{

for (auto it : SelectionVector) {

std::string command = "submod -name " + it.first;

Pass::call_on_selection(design, it.second, command);

}

}

Вам определенно не нужно (и не нужно) изменять selection_stack,

Мне было интересно, есть ли какая-либо утилита /API внутри источника yosys, которая принимает вектор ячеек (а также подмодуль имени) и помещает их в подмодуль.

Вы бы сделали это, установив submod="<name>" атрибут на клетках. Тогда просто запустите submod команда.

Вы могли видеть, что scc документация упоминает -set_attr вариант, который пока не реализован. Теперь я реализовал эту опцию в коммите ef603c6 (совершить 914aa8a содержит исправление для scc).

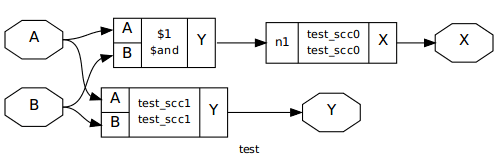

С помощью этой функции вы можете теперь выполнить то, что вы описали, используя что-то вроде следующего скрипта yosys.

read_verilog test.v

prep

scc -set_attr submod scc{}

submod

show test

Я проверил это с фоллингом test.v файл:

module test(input A, B, output X, Y);

assign X = (A & B) ^ X, Y = A | (B ^ Y);

endmodule

3. Executing SCC pass (detecting logic loops).

Found an SCC: $xor$test.v:2$2

Found an SCC: $or$test.v:2$4 $xor$test.v:2$3

Found 2 SCCs in module test.

Found 2 SCCs.