Как записать на два выходных порта изнутри архитектуры в VHDL?

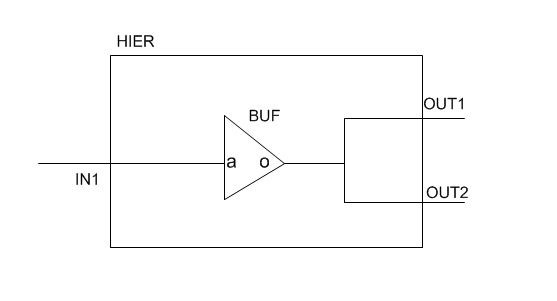

Я столкнулся с проблемой при попытке подключить компонент к двум выходным портам родительской иерархии в VHDL. Поскольку физическое соединение может быть выполнено только с помощью оператора "port port", нет возможности подключить локальный сигнал к более чем одному выходному порту. Вот пример:

Описание вышеуказанной схемы должно быть чем-то. как это:

entity HIER is

port (

IN1 : in bit;

OUT1, OUT2 : out bit);

end hier;

architecture HIER_IMPL of HIER is

component BUF is

port (a : in bit; o : out bit);

end component;

begin

BUF1 : BUF port map (a => IN1, o => OUT1, o => OUT2);

end HIER_IMPL;

Однако двойное назначение выходного порта "o" для OUT1 и OUT2 не будет работать, поскольку это запрещено в VHDL.

1 ответ

Есть ли причина, по которой вы не можете создать внутренний сигнал и использовать этот сигнал для управления двумя выходными портами, как это?

entity HIER is

port (

IN1 : in bit;

OUT1, OUT2 : out bit);

end hier;

architecture HIER_IMPL of HIER is

signal temp : bit;

component BUF is

port (a : in bit; o : out bit);

end component;

begin

BUF1 : BUF port map (a => IN1, o => temp);

OUT1 <= temp;

OUT2 <= temp;

end HIER_IMPL;

Если это невозможно, как насчет этого?

entity HIER is

port (

IN1 : in bit;

OUT1, OUT2 : out bit);

end hier;

architecture HIER_IMPL of HIER is

component BUF is

port (a : in bit; o : out bit);

end component;

begin

BUF1 : BUF port map (a => IN1, o => OUT1);

BUF2 : BUF port map (a => IN1, o => OUT2);

end HIER_IMPL;