Расовые условия

В настоящее время я застрял, пытаясь понять две вещи, связанные с условиями гонки.

Выпуск 1:

Мне был задан следующий вопрос:

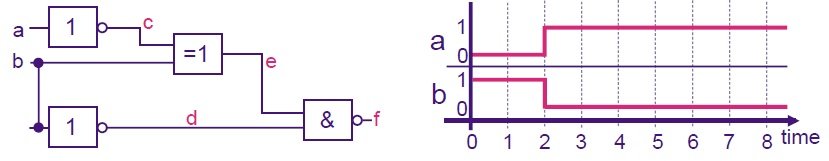

We consider the digital circuit and the value of its inputs a,

and b as given below. For all logic gates, we assume that

there is a gate delay of exactly one time unit (i.e. the gate

delay equals the time between two dotted lines in the

diagram). Give the values of c, d, e, f in the digital circuit for

every point of time between 0 and 8.

И ответ дается следующим образом:

Как именно это достигается? Это то, что я думаю до сих пор:

- с начинается с 1, потому что начинается с 0

- d начинается с 0, потому что b начинается с 1

- Когда время равно 2 a становится 1... есть задержка распространения 1 для c, чтобы переключиться на 0, следовательно, она становится 0 в 3 единицах времени

- Та же логика применима к

- e и f должны быть постоянными 1 или 0, но, похоже, что-то на них влияют.

Что на самом деле здесь происходит? Связано ли это с булевой функцией или чем-то подобным. Если да, то?

Выпуск 2:

У кого-нибудь есть простой способ или логический подход для создания простой схемы (используя логические функции XOR, AND, OR, NOT, NAND с:

- статическое состояние гонки - когда значение должно быть постоянным

- динамическое состояние гонки - когда ожидается изменение значения

Спасибо заранее!

1 ответ

Итак, условия гонки в асинхронных цепях возникают, когда входы меняются в разное время для шлюза. Допустим, ваша логическая функция выглядит так

λ = ab + ~b~a

самый простой способ реализовать эту функцию с воротами выглядит так

ПРИМЕЧАНИЕ. Я предполагаю, что ваши основные строительные блоки - это И, ИЛИ, и НЕ. Очевидно, что в схемах CMOS NAND, NOR и NOT - это то, как вы строите схемы, но общий принцип остается тем же. Я также предполагаю, что AND, NOR и NOT имеют одинаковую задержку, когда на самом деле NAND и NOR имеют разные задержки, если выходные данные имеют вид 0 to 1 или же 1 to 0и NOT примерно на 20% быстрее, чем NAND или NOR.

a ->| AND |-------->| OR | -> λ

b ->| 1 | | |

| |

a ->| NOT |->|AND|->| |

b ->| NOT |->| 2 | | |

Теперь предположим, что AND и NOT оба имеют задержку 2 нс. Это означает, что логический элемент ИЛИ видит значение при изменении его первой позиции за 2 нс до того, как он видит значение при изменении его второй позиции.

Что означает, что если a а также b оба уходят от 1 в 0, вы ожидаете λ остаться прежним, так как выход первых логических элементов И 1 в 0, но вывод логического элемента И идет от 0 в 1означает, что условие ИЛИ остается верным.

Тем не менее, если вы получите выход из второго вентиля AND немного позже первого вентиля AND, то ваш вентиль OR на мгновение увидит 0,0 на его входе при переходе от 1,0 в 0,1, Что значит λ будет иметь мгновенное падение, и это будет выглядеть

__

a |___________

__

b |___________

____

AND1 |_________

_______

AND2 ______|

______ _____

λ |_|

Если вы посмотрите на входы логического элемента ИЛИ прямо между падением AND1 и повышением AND2, оно распространит 0 через шлюз ИЛИ, и, конечно же, через 2 нс происходит падение на выходе.

Это общий обзор того, как возникают условия гонки. Надеюсь, что это поможет вам понять ваш вопрос.