Задание ограничений в решетке FPGA

Я работаю над проектом, включающим Lattice XP2-30E FPGA и аналого-цифровой преобразователь AD9238. Задержка распространения от CLK до DATA рекламного конвертера указана в таблице данных как:

- t_pd_ad_min = 2ns

- t_pd_ad_max = 6ns.

Кроме того, задержка платы

- t_pd_board_min = 0,5 нс

- t_pd_board_max = 1ns

Основные тактовые частоты (80 МГц /12,5 нс) FPGA распределяются от внутреннего делителя тактовых импульсов и используются для генерации тактовых импульсов для АЦП.

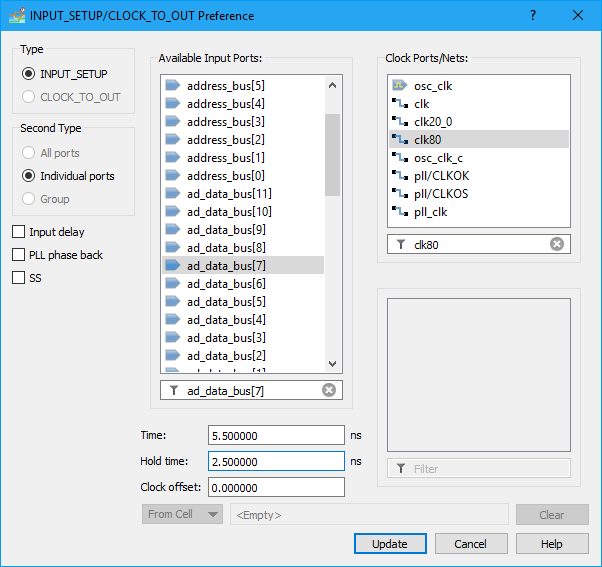

Как мне указать время установки и удержания для порта данных FPGA относительно тактового сигнала АЦП? Я сделал несколько попыток без успеха. Представление "Электронная таблица / Настройки времени", которое я использовал для указания INPUT_SETUP показано на рисунке ниже

Как видно из рисунка, я могу использовать только clk80 в качестве эталона (который является выходом делителя тактового сигнала). Между этими часами и часами, управляющими АЦП, имеется значительный сдвиг фаз в результате задержки от делителя тактовых импульсов к выходному выводу ПЛИС. Как учесть эту задержку при указании предпочтений?