Код Хэмминга (7,4) - конечный автомат

Поэтому я работаю над лабораторным заданием на урок информатики. У меня назначенное задание, и я пытаюсь получить всю возможную помощь, что касается профессора, мне нужно подождать несколько дней, прежде чем я смогу обратиться к ним за помощью. Так что я вижу, смогу ли я помочь ей.

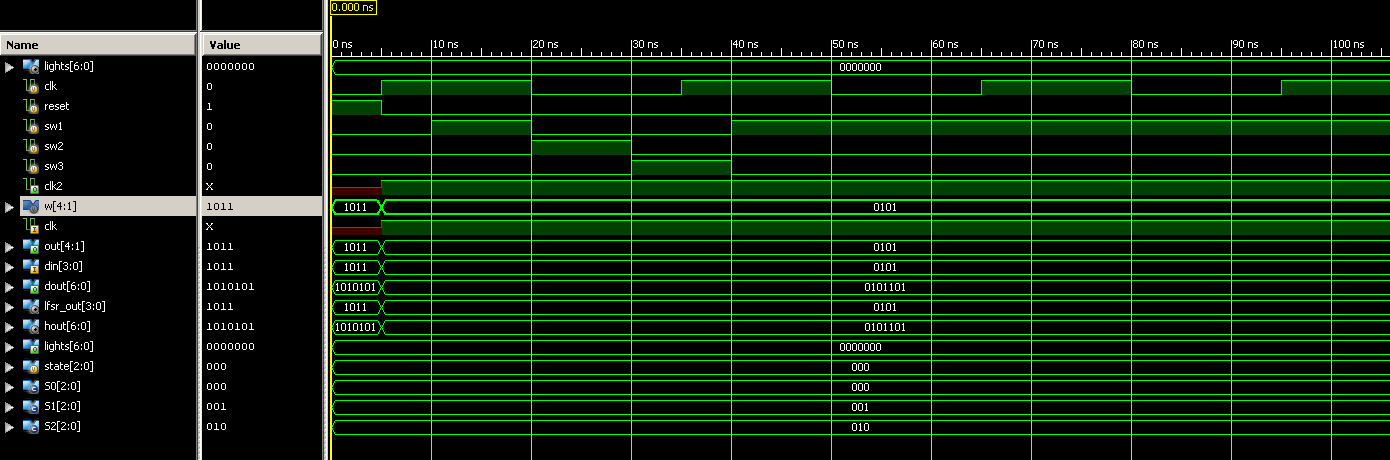

Моя проблема в том, что мой конечный автомат не работает так, как он должен быть задан в лабораторном задании. Конечный автомат должен иметь 3 состояния; холостой ход, s1, s2. Предполагается, что в режиме ожидания все нули отображаются в форме сигнала, в состоянии 1 будет отображаться случайно сгенерированное 4-битное число из LFSR, а в состоянии 2 будет показан результат из 4-битного числа после того, как Хемминга (7,4) выполнено. Часы изменяются на часы с частотой 1 Гц, используется деление clk.

Код выглядит следующим образом:

CLOCK_1HZ

module clock_1hz (clk, reset, clk2);

input clk, reset;

output clk2;

reg temp;

reg [25:0] cnt;

always @(posedge clk or posedge reset)

begin

if (reset)

begin

cnt = {25{1'b0}};

end

else

begin

if (cnt == 26'b10111110101111000001111111)

begin

cnt = {25{1'b0}};

temp = 1'b1;

end

else if (cnt < 26'b01011111010111100000111111)

begin

cnt = cnt + 1;

temp = 1'b1;

end

else

begin

cnt = cnt + 1;

temp = 1'b0;

end

end

end

assign clk2 = temp;

endmodule

ЛРСОС

module lfsr (out, clk, rst);

output [4:1] out;

input clk, rst;

reg [4:1] w;

always @(posedge clk or posedge rst)

begin

if (rst)

begin

w = 4'b1011;

end

else

w = {w[3],w[2],w[1]^w[4], w[4]};

end

assign out=w;

endmodule

Хэмминга

module hamming(din, dout);

output [6:0] dout;

input [3:0] din;

assign dout[6] = din[3];

assign dout[5] = din[2];

assign dout[4] = din[1];

assign dout[3] = din[1] ^ din[2] ^ din[3];

assign dout[2] = din[0];

assign dout[1] = din[0] ^ din[2] ^ din[3];

assign dout[0] = din[0] ^ din[1] ^ din[3];

endmodule

Весь этот код работает правильно и вычисляет правильный HAMMING, а деление часов хорошо работает с LFSR и работает, когда оно комбинируется как иерархическая структура.

Когда я делаю FSM для этого кода, он работает до вычисления числа Хемминга, но не меняет состояние, когда указано.

- Когда переключатель 1 установлен: состояние IDLE

- Когда переключатель 2 установлен: состояние 1, показывает 4-битный номер LFSR

- Когда переключатель 2 установлен: состояние 2, показывает 7-битный результат Хэмминга

Ниже приведен мой код для конечного автомата, а за ним - выходной сигнал.

module fsm ( clk , reset , sw1 , sw2 , sw3 , lights );

input clk, reset, sw1, sw2, sw3;

output reg [6:0] lights;

reg[2:0] state;

wire clkhz;

wire [3:0] lfsr_out;

wire [6:0] hout;

parameter S0 = 3'b000, S1 =3'b001, S2 = 3'b010; // states

clock_1hz u1(.clk(clk),

.reset(reset),

.clk2(clkhz));

lfsr u2(.rst(reset),

.clk(clkhz),

.out(lfsr_out));

hamming u3(.din(lfsr_out),

.dout(hout));

always @(posedge clk or posedge reset)

begin

if (reset == 1)

begin

state <= S0;

end

else

case(state)

S0: if(sw1 == 1)

begin

state <= S0;

end

S1: if(sw2 == 1)

begin

state <= S1;

end

S2: if(sw3 == 1)

begin

state <= S2;

end

default state <= S0;

endcase

end

always @(*)

begin

case(state)

S0: lights = 7'b0000000; //led are all off

S1: lights = lfsr_out; //4bit lfsr shown on led

S2: lights = hout; // display hamming code result

default lights = 7'b0000000; //led are all off

endcase

end

endmodule

ВОЛНА КОНЕЧНОГО ГОСУДАРСТВЕННОГО СТАНКА:

1 ответ

Я не думаю, что здесь нужен конечный автомат. От вас описание требований, может быть, вам просто нужно запомнить текущий переключатель нажат? Если это так, вы можете сделать что-то вроде:

always @(posedge clk or posedge reset)

if (reset == 1)

state <= S0;

else

if (sw1)

state <= S0;

else if (sw2)

state <= S1;

else if (sw3)

state <= S2;

Сейчас state запоминает текущий переключатель нажат. Исходя из вашего описания требований, выполнение этого, по-видимому, не зависит от того, какой переключатель какой переключатель был нажат до этого, и, следовательно, не похоже, что вам нужен конечный автомат - поведение не зависит от состояния.

(Вам не нужны все эти beginс и endс, либо. Они вам не нужны, если в ветке только одно утверждение.)