Как загрузить устаревшую версию BIOS (coreboot) в клиентском ядре Simics QSP?

Я использую Simics 6.0.83 (Public Release Preview) с целью, определенной на основе qsp-client-core.simics, и пытаюсь загрузить двоичный файл coreboot как устаревший BIOS.

Конфигурация, которую я пытаюсь:

# In order to run this, the QSP-x86 (2096), QSP-CPU (8112) and

# QSP-Clear-Linux (4094) packages should be installed.

decl {

! Script that runs the Quick Start Platform (QSP) with a client processor core.

params from "%simics%/targets/qsp-x86/qsp-clear-linux.simics"

default cpu_comp_class = "x86-coffee-lake"

default num_cores = 4

default enable_efi = FALSE

default bios_image = "/home/debian/dasharo/coreboot/build/coreboot.rom"

}

run-command-file "%simics%/targets/qsp-x86/qsp-clear-linux.simics"

При попытке

run-command-file из simics CLI я получаю:

[board.mb.cpu0.core[0][0] unimpl] Warning: Cache flush without writeback (will not warn again for this CPU).

[board.mb.cpu0.core[0][0] info] CAR segment [0xfef00000: 0xfef40000] added to board.mb.cpu0.mem[0][0]

[board.mb.cpu0.core[0][0] info] 0xc91: Writing to unknown MSR. Signaling GP fault.

[board.mb.cpu0.core[0][0] info] Exception 13 while calling the double fault handler. Triple fault.

Breaking on triple fault. Break on triple fault is controlled by the break_on_triple_fault attribute.

Как я могу попробовать coreboot в Simics?

3 ответа

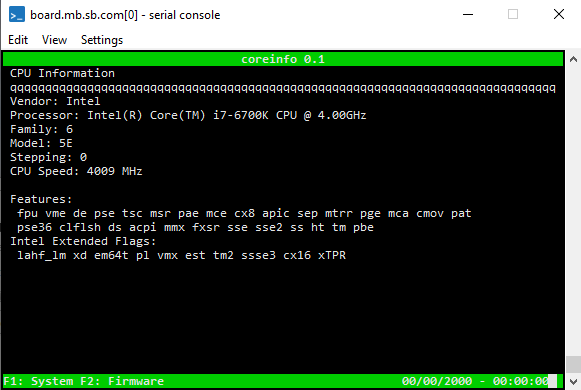

Мне любопытно, поэтому клонирован, построен и загружен coreboot с coreinfo в качестве полезной нагрузки на основе https://doc.coreboot.org/tutorial/part1.html

Может быть, вы можете проверить мой defconfig, как показано ниже

Похоже, вам нужно отладить, почему CoreBoot не работает с моделью. Предложите включить отметки времени для журналов (настройка журнала-отметка времени), чтобы увидеть, связано ли MSR с тройной ошибкой. Также попробуйте трассировку исключения во время возникновения проблемы, чтобы увидеть, какие исключения задействованы. Если вы создали двоичный файл самостоятельно, применение отладчика к нему должно быть простым.

О ведении журнала: Как мне получить отметки времени в сообщениях журнала Simics?

Обратите внимание, что CoreBoot может потребоваться для поддержки используемого варианта ядра процессора. Указанный в качестве примера MSR недоступен для "Coffee Lake". Но это может быть просто CoreBoot, исследующий доступные функции.

Если вы хотите использовать небольшой загрузчик, попробуйте SlimBootLoader с открытым исходным кодом по адресу https://slimbootloader.github.io/supported-hardware/qsp.html.

Я понятия не имею, почему Coreboot касается 0xc91 (который является частью технологии Intel Resource Director Technology (Intel RDT) и, очевидно, имеет другое назначение, не связанное с кэш-памятью). Однако попробуйте следующее:

- проверить текущий процессор

simics> pselect "board.mb.cpu0.core[0][0]

- найти адресное пространство, в котором отображаются MSR:

simics> board.mb.cpu0.core[0][0]->cpu_msr_spaceboard.mb.cpu0.cpu_msr[0][0]

- сопоставления поиска:

simics> board.mb.cpu0.cpu_msr[0][0].map

не найдено сопоставление на 0xc91

поскольку в Simics есть инструменты для разработки моделей — создайте простую модель устройства, реализующую отсутствующие регистры.

сопоставьте такое устройство с пространством MSR, используя:

board.mb.cpu0.cpu_msr[0][0].добавить карту

В качестве альтернативы вы можете установить цель по умолчанию для пространства MSR — в этом случае все отсутствующие доступы (как чтение, так и запись) попадут в нее:

simics> @ always_zeroes = SIM_create_object("set-memory", "zeroes", [["value", 0]])

simics> @ conf.board.mb.cpu0.cpu_msr[0][0].default_target = [always_zeroes, 0, 0, None]

Первая строка создает модель класса set-memory, которая представляет собой простое устройство, которое всегда возвращает свое значение (в этом примере значение равно нулю) и игнорирует записи.

Вторая строка устанавливает цель по умолчанию для адресного пространства MSR, так что все отсутствующие обращения идут к

always_zeroesустройство.

Обратите внимание, что последний вариант не обеспечит логику cache-as-ram, как на реальном оборудовании, но поможет вам пройти дальше. В любом случае, функциональная модель процессора в Simics не реализует кеши, как в аппаратном обеспечении.