Как процессор делает запрос данных через TLB и кеш?

Я наблюдаю за несколькими последними микроархитектурами Intel (Nehalem/SB/IB и Haswell). Я пытаюсь понять, что происходит (на довольно упрощенном уровне), когда делается запрос данных. Пока у меня есть эта грубая идея:

- Механизм выполнения делает запрос данных

- "Управление памятью" запрашивает L1 DTLB

- Если вышеупомянутое пропускает, L2 TLB теперь запрашивается

В этот момент могут произойти две вещи, промах или попадание:

Если его попадание, то CPU пытается использовать кэши L1D/L2/L3, таблицу страниц, а затем основную память / жесткий диск в таком порядке?

Если ошибка, то ЦП запрашивает (встроенный контроллер памяти?) Запросить проверку таблицы страниц, хранящейся в ОЗУ (правильно ли я получил роль IMC?).

Если бы кто-то мог отредактировать / предоставить набор маркеров, которые предоставляют базовый "обзор" того, что процессор делает из запроса данных механизма выполнения, включая

- L1 DTLB (данные TLB)

- L2 TLB (данные + инструкция TLB)

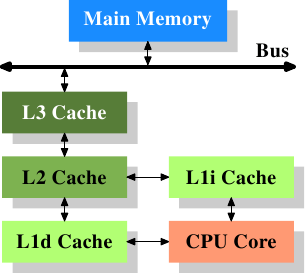

- L1D Cache (кэш данных)

- L2 кеш (данные + кеш инструкций)

- L3 кеш (данные + кеш инструкций)

- Часть процессора, которая контролирует доступ к основной памяти

- Таблица страниц

это будет наиболее ценно. Я нашел несколько полезных изображений:

- http://www.realworldtech.com/wp-content/uploads/2012/10/haswell-41.png

- http://upload.wikimedia.org/wikipedia/commons/thumb/6/60/Intel_Core2_arch.svg/1052px-Intel_Core2_arch.svg.png

но они на самом деле не разделяли взаимодействие между TLB и кешами.

ОБНОВЛЕНИЕ: изменили вышеупомянутое, как я думаю, теперь я понимаю. TLB просто получает физический адрес от виртуального. Если есть промах - у нас проблемы, и нам нужно проверить таблицу страниц. Если есть попадание, мы просто проходим вниз по иерархии памяти, начиная с L1D-кэша.

2 ответа

Карта страницы применима только для преобразования виртуальных адресов в физические. Однако, поскольку он находится в памяти и только частично кэшируется в TLB, вам, возможно, придется получить к нему доступ во время процесса перевода.

Основной поток выглядит следующим образом:

- Выполнение вычисляет адрес (фактически некоторые вычисления, такие как масштаб и смещения, могут быть выполнены в блоке памяти).

- Поиск в DTLB

2.а Если пропущено, ищите в TLB 2-го уровня.

2.aa если пропустил - начни ходить по странице.

2.ab при попадании в TLB 2-го уровня, заполните DTLB и перейдите к новому физическому адресу

2.b. ударил в DTLB перейти на физический адрес - Поиск L1, если пропущен - ищите L2, если пропустил, снова ищите L3, если пропустил - отправьте на контроллер памяти, дождитесь доступа к DRAM.

- Когда данные возвращаются (с любого уровня), пополняйте кеши по пути (в зависимости от политики заполнения, инклюзивности кеша, спецификаций временности команд, типа области памяти и, возможно, других факторов).

Если требуется переход на страницу, остановите основной запрос и выполните физические нагрузки на карту страницы (в соответствии с архитектурным определением). В x86 он может включать в себя CR3, PDPTR, PDP, PDE, PTE и т. Д., В зависимости от режима подкачки, размеров страниц и т. Д. Обратите внимание, что при виртуализации для каждого уровня просмотра страниц в виртуальной машине может потребоваться полный просмотр страниц на хосте (так что вы на самом деле квадрат количество необходимых шагов).

Обратите внимание, что карта страницы в основном представляет собой древовидную структуру, где каждый доступ зависит от значения предыдущего (и части виртуального адреса, который вы переводите). Следовательно, эти обращения зависят, и только после завершения последнего вы получите физический адрес и сможете вернуться к #3. Все это время строка, которую вы хотите, может находиться в вашем L1, и вы не сможете знать (хотя, если честно, если вы сделали просмотр страницы, у вас вряд ли будет линия в верхнем кэше).

Другие важные замечания - карта страницы находится в физическом пространстве и доступна таким образом. Вы не хотите переводить доступы, которые вам нужны для перевода, это может быть тупиком:)

Что еще более важно, данные карты страницы могут быть кэшированы, поэтому, хотя простой доступ к памяти может быть расширен до нескольких из-за пропуска TLB, просмотр страницы может все еще быть довольно дешевым.

Да, как объяснено в длинном описании здесь:

http://lwn.net/Articles/252125/

наглядно проиллюстрирован переход от ЦП к L1 к L2 к L3.