Как выполнить сдвиг вправо двоичного умножения?

1 ответ

Решение

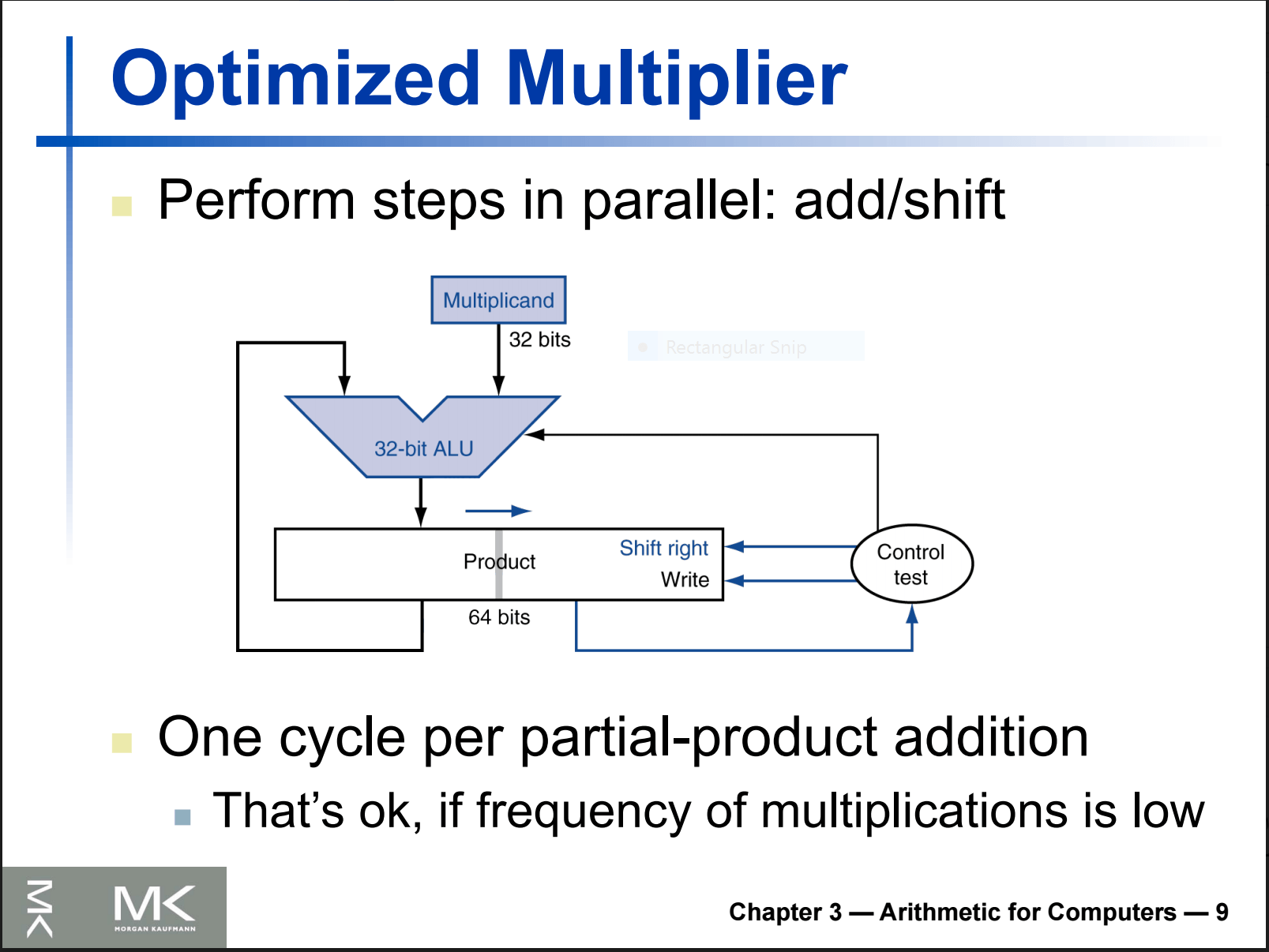

Пример умножается. Примечание. 4-битный сумматор выдает 5-битную сумму (старший бит - перенос). Вход для сумматора умножается на плюс 3–6 битов регистра продукта, сумма, включая перенос, идет в биты 3–7 регистра продукта.

multiplicand 1100, multiplier 0101

7 6 5 4 3 2 1 0 product bit index

0 0 0 0 0 1 0 1 initial 8 bit register

0 0 0 0 0 0 1 0 1 shift right, 1 bit shifted out

1 1 0 0 add multiplicand

0 1 1 0 0 0 1 0

0 0 1 1 0 0 0 1 0 shift right, 0 bit shifted out

0 0 0 0 no add

0 0 1 1 0 0 0 1

0 0 0 1 1 0 0 0 1 shift right, 1 bit shifted out

1 1 0 0 add multiplicand

0 1 1 1 1 0 0 0

0 0 1 1 1 1 0 0 0 shift right, 0 bit shifted out

0 0 0 0 no add

0 0 1 1 1 1 0 0

multiplicand 1111, multiplier 1111

0 0 0 0 1 1 1 1 initial 8 bit register

0 0 0 0 0 1 1 1 1 shift right, 1 bit shifted out

1 1 1 1 add multiplicand

0 1 1 1 1 1 1 1

0 0 1 1 1 1 1 1 1 shift right, 1 bit shifted out

1 1 1 1 add multiplicand

1 0 1 1 0 1 1 1

0 1 0 1 1 0 1 1 1 shift right, 1 bit shifted out

1 1 1 1 add multiplicand

1 1 0 1 0 0 1 1

0 1 1 0 1 0 0 1 1 shift right, 1 bit shifted out

1 1 1 1 add multiplicand

1 1 1 0 0 0 0 1