Почему в 64-битном виртуальном адресе 4 коротких (48-битных) по сравнению с физическим адресом (52-битном)?

В книге "Программирование низкого уровня: C, сборка и выполнение программы на архитектуре Intel® 64" я прочитал:

Каждый виртуальный 64-битный адрес (например, тот, который мы используем в наших программах) состоит из нескольких полей. На самом деле адрес имеет ширину всего 48 бит; он расширяется до 64-битного канонического адреса. Его характеристика в том, что его 17 левых битов равны. Если условие не выполняется, адрес сразу же отклоняется при использовании. Затем 48 бит виртуального адреса преобразуются в 52 бита физического адреса с помощью специальных таблиц.

Почему разница в 4 бита между виртуальным адресом и физическим адресом?

2 ответа

Я полагаю, что вы говорите о x86-64, мой ответ основан на этой архитектуре.

При работе в 64-битном режиме ЦП использует обновленную функцию для преобразования виртуальных адресов в физические адреса, известные как PAE - расширение физических адресов.

Первоначально изобретенная для преодоления ограничения в 4 ГБ при использовании 32-разрядных указателей, эта функция предполагает использование таблиц 4-го уровня.

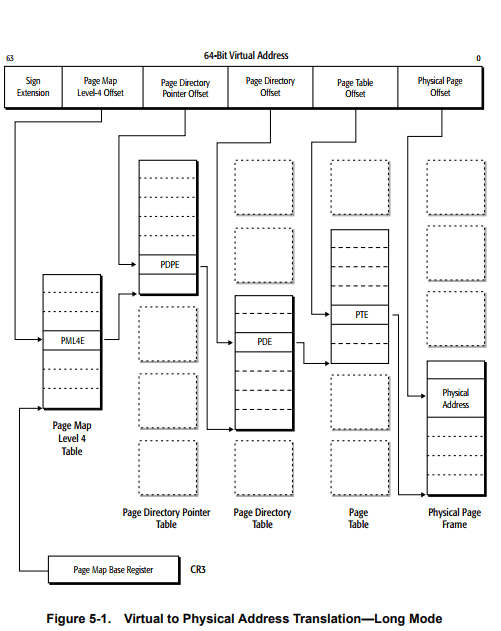

Каждая таблица дает указатель на следующую таблицу, вплоть до самой правой, которая дает старшие биты физического адреса. Чтобы получить представление об этой картине из Руководства по программированию архитектуры AMD64:

Основанием для всех этих таблиц является разреженность: метаданные для преобразования виртуальных адресов в физические адреса огромны - если бы мы использовали только 4 КБ страницы, нам потребовалось бы 264 - 12 = 252 записи, чтобы охватить все 64-битное адресное пространство,

Таблицы допускают разреженный подход, только необходимые записи заполняются в памяти.

Эта схема отражена в том, как виртуальный адрес разделен (и, следовательно, косвенно, по количеству уровней), только индексы из 9 бит используются для индексации таблиц на каждом уровне.

Начиная с включенного бита 12, это дает: уровень 1 -> 12-20, уровень 2 -> 21-29, уровень 3 -> 30-38, уровень 4 -> 39-47.

Это объясняет текущий предел реализации только 48 бит виртуального адресного пространства.

Обратите внимание, что на уровне команд, где используются логические адреса, мы полностью поддерживаем 64-битные адреса.

Полная поддержка также доступна на уровне сегментации, части, которая переводит логические адреса в линейные адреса.

Таким образом, ограничение исходит от PAE.

Мое личное мнение заключается в том, что AMD поспешила стать первой, кто выпустил процессор x86 с 64-битной поддержкой и повторно использовал PAE, исправляя его с новым уровнем косвенности для преобразования до 48 бит.

Обратите внимание, что как Intel, так и AMD позволяют будущей реализации использовать 64-битный виртуальный адрес (возможно, с большим количеством таблиц).

Однако обе компании установили жесткий предел в 52 бита для физического адреса. Зачем?

Ответ все еще можно найти в том, как работает пейджинг.

В 32-битном режиме каждая запись в каждой таблице имеет ширину 32 бита; младшие биты используются в качестве флагов (поскольку требования выравнивания делают их бесполезными для процесса перевода), но старшие биты были использованы для перевода, обеспечивая виртуальный / физический перевод 32/32.

Важно подчеркнуть, что использовались все 32 бита, в то время как некоторые младшие биты не использовались в качестве флагов, Intel пометила их как "Игнорируемые" или "Доступные", что означает, что ОС может их свободно использовать.

Когда Intel представила PAE, им потребовалось еще 4 бита (тогда PAE составлял 36 бит), и логично было удвоить размер каждой записи, поскольку это создает более эффективную компоновку, чем, скажем, 40-битная запись таблицы.

Это дало Intel много свободного места, и они отметили его как зарезервированное (это можно лучше наблюдать в более старых версиях руководств Intel SDM, таких как эта).

Со временем в записи потребовались новые атрибуты, наиболее известным из которых был бит XD/NX.

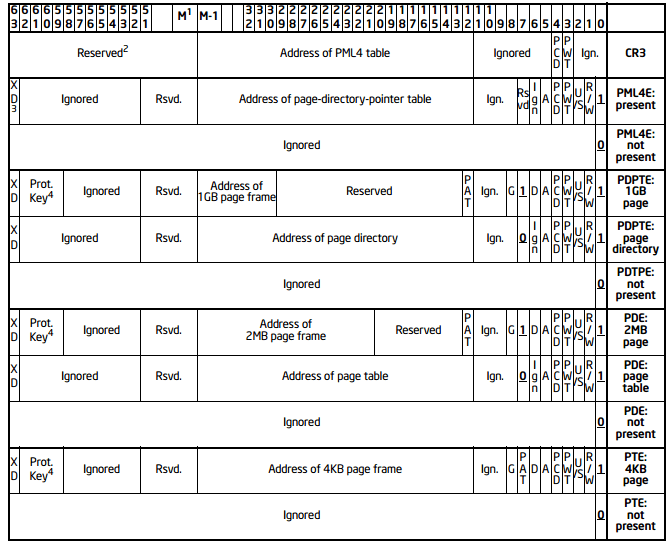

Защитные ключи также являются относительно новой функцией, которая занимает место в записи. Это показывает, что полная 64/64 битная виртуальная / физическая трансляция больше невозможна с текущим ISA.

Для наглядности приведен формат записей 64-битной таблицы PAE:

Это показывает, что 64-разрядный физический адрес невозможен (для больших страниц все еще есть способ исправить это, но учитывая расположение битов, которое кажется маловероятным), но не объясняет, почему AMD установила ограничение в 52 бита.

Ну, сложно сказать.

Конечно, размер физического адресного пространства связан с некоторыми аппаратными затратами: больше выводов (хотя со встроенным контроллером памяти это уменьшается, поскольку спецификации DDR мультиплексируют много сигналов) и больше места в кэш-памяти /TLB.

На этот вопрос (похожий, но недостаточно сделать дубликат) ответ города Википедии, который в свою очередь якобы ссылается на AMD, утверждая, что инженеры AMD установили ограничение в 52 бита после должных соображений о преимуществах и затратах.

Я делюсь тем, что написал Ханс Пассант более 6 лет назад: существующие механизмы разбиения на страницы не подходят для полной 64-битной физической адресации, и это, вероятно, причина, по которой и Intel, и AMD никогда не беспокоились о сохранении старших бит в каждой записи.

Обе компании знают, что когда технология приблизится к 52-битному пределу, она также будет сильно отличаться от ее фактической формы.

К тому времени они разработают лучший механизм для памяти в целом, чтобы избежать чрезмерного проектирования существующего.

В более раннем ответе говорится

Конечно, размер физического адресного пространства связан с некоторыми аппаратными затратами: больше контактов [...] и больше места в кешах/TLB.

что предполагает неправильное представление автора: процессоры x86-64 на самом деле имеют достаточно контактов для адресации 252 байт ОЗУ.

На самом деле, ни один из когда-либо выпущенных процессоров не имел такого большого физического адресного пространства. Сокеты его не поддерживают, и (поэтому) для него не нужны ни биты в кеше, ни TLB.

Единственный смысл, в котором адресное пространство составляет 52 бита, заключается в том, что некоторые биты в записях таблицы страниц помечены как зарезервированные (это означает, что ОС должна установить их в 0), а другие помечены как игнорируемые (это означает, что ОС может использовать их для свои цели). Зарезервированных битов достаточно, чтобы в будущем расширить физическое адресное пространство до 252 байтов, хотя в принципе им можно было бы присвоить и другие роли.

Компромисс назначения битов как зарезервированных/игнорируемых:

Меньшее количество игнорируемых битов означает, что операционные системы могут хранить там меньше информации, что может сделать их медленнее в наши дни.

Меньшее количество зарезервированных битов означает, что формат записи в таблице страниц, возможно, придется изменить еще раз, когда будет исчерпан предел физического адресного пространства, спустя годы.

32-разрядные процессоры x86 в течение многих лет имели 36-разрядное физическое адресное пространство, поэтому возможно иметь физическое адресное пространство больше, чем виртуальное, но это неудобно на уровне ОС. Я не верю, что есть какие-либо планы по выпуску процессора x86-64 с физическим адресным пространством, большим, чем виртуальное. Intel недавно представила 5-уровневую подкачку , которая увеличивает виртуальное адресное пространство до 257 байт . В их официальном документе говорится о размере физического адреса процессоров Intel, возвращаемом CPUID с EAX=80000008h:

Процессоры, поддерживающие архитектуру Intel 64, имеют для этого значения не более 46. Ожидается, что процессоры, поддерживающие 5-уровневую подкачку, будут перечислять более высокие значения, вплоть до 52.

Из этого я делаю вывод, что на данный момент у них нет планов по изменению формата таблицы страниц для поддержки более 252 байт ОЗУ, а также у них нет планов по поддержке физического адресного пространства, превышающего 1/4 виртуального адресного пространства. . Последнее имеет смысл, потому что только половина виртуального адресного пространства предназначена для ядра, а его полное заполнение оперативной памятью, вероятно, было бы неудобно.

Руководство по архитектуре AMD, том 2, ред. 3.38 (ноябрь 2021 г.) говорит

[T] механизм перевода страниц может быть расширен для поддержки 52-битных физических адресов. [...] В настоящее время архитектура AMD64 поддерживает 40-битные адреса в этом режиме, что позволяет поддерживать до 1 терабайта пространства физических адресов.

У AMD пока нет 5-уровневого пейджинга.