Может ли 1 ядро CUDA обрабатывать более 1 инструкции с плавающей запятой за такт (Максвелл)?

Список графических процессоров Nvidia - GeForce 900 Series - там написано, что:

4 Производительность одинарной точности рассчитывается как 2-кратное число шейдеров, умноженное на базовую тактовую частоту ядра.

Т.е. например для GeForce GTX 970 мы можем рассчитать производительность:

1664 ядер * 1050 МГц * 2 = 3 494 пиковых флопов (3 494 400 мфлопс)

Это значение мы видим в столбце - Мощность обработки (пиковая) GFLOPS - Single Precision.

Но почему мы должны умножить на 2?

Там написано: http://devblogs.nvidia.com/parallelforall/maxwell-most-advanced-cuda-gpu-ever-made/

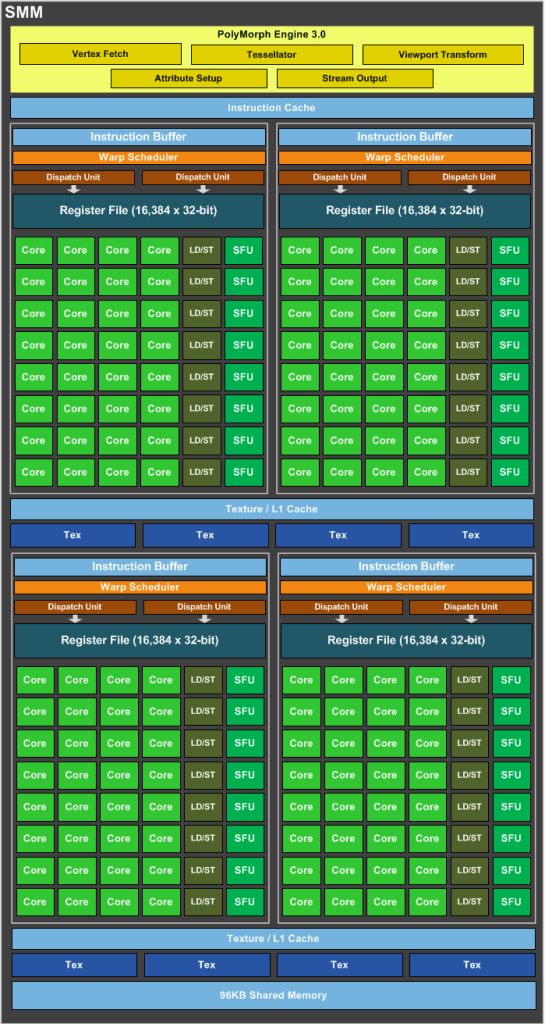

SMM использует конструкцию на основе квадрантов с четырьмя 32-ядерными блоками обработки, каждый с выделенным планировщиком деформации, способным отправлять две инструкции за такт.

Хорошо, nVidia Maxwell - это суперскалярная архитектура, которая отправляет две инструкции за такт, но может ли 1 ядро CUDA (FP32-ALU) обрабатывать более 1 инструкции за такт?

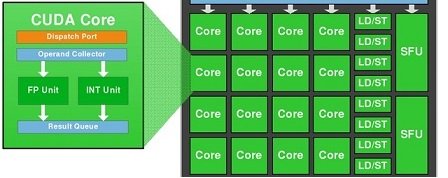

Мы знаем, что 1 ядро CUDA содержит два блока: блок FP32 и блок INT. Но INT-модуль не имеет отношения к GFlops (операций сплавающей точкой в секунду).

Т.е. один СММ содержит:

- 128 FP32-блок

- 128 INT-блок

- 32 SFU-единицы

- 32 LD/ST-блок

Для получения префоманса в GFlops нам нужно использовать только: 128 FP32-блоков и 32 SFU-блока.

Т.е. если мы одновременно используем как 128 модулей FP32, так и 32 модуля SFU, то мы можем получить 160 инструкций с операциями с плавающей запятой за такт на 1 СМ.

Т.е. мы должны умножить на 1,2 = (160/132) вместо 2.

1664 ядер * 1050 МГц * 1,2 = 2096 пиков GFlops

Зачем писать в вики, что мы должны умножить число ядер * МГц на 2?

1 ответ

"Ядро" CUDA (также называемое SP) чаще всего относится к единицам с плавающей запятой одинарной точности в SM (потоковом мультипроцессоре). Ядро CUDA может инициировать одну инструкцию с плавающей запятой одинарной точности за такт. (Устройство конвейерно, поэтому оно может инициировать одну инструкцию за такт и может удалить одну инструкцию за такт, но не может полностью обработать данную инструкцию в данном такте.)

Если эта команда, например, представляет собой сложение с одинарной точностью или умножение с одинарной точностью, то это ядро может вносить одну операцию с плавающей запятой за такт, поскольку сложение или умножение считается одной операцией с плавающей запятой. Если, с другой стороны, инструкция является инструкцией FMA (умножение-сложение с плавающей запятой), то ядро выполнит операцию умножения с плавающей запятой и операцию сложения с плавающей запятой за один и тот же период времени. Это означает, что фактически две операции выполняются одной инструкцией. Такое использование FMA дает множитель 2 при вычислении максимальной теоретической пропускной способности.

Таким образом, ядро может обрабатывать (то есть инициировать, удалять) только одну инструкцию за такт, но если эта инструкция является FMA, она считается двумя операциями с плавающей запятой.