Ошибка встроенной сборки ARM GCC для операнда%w

У меня есть сегмент встроенной сборки ARMv8:

/* get leading 0 of cache ways */

__asm__ __volatile__

(

"CLZ %w[shift], %w[maxWay] \n"

: [shift] "=r" (uiShift)

: [maxWay] "r" (uiMaxWay)

);

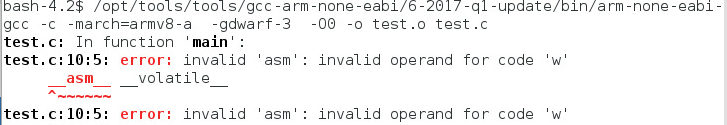

При компиляции компилятором ARM GCC:

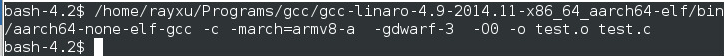

Интересно, что если я скомпилирую с компилятором Linaro, то проблем нет.

Есть ли проблема в компиляторе ARM GCC или в моем коде?

1 ответ

В отличие от x86, где один и тот же компилятор может создавать код x86-32 или x86-64 с -m32 а также -m64вам нужна отдельная сборка gcc для ARM против AArch64.

ARM GCC принимает -march=armv8-a, но он все еще компилируется в 32-битном режиме ARM, а не в AArch64.

Я могу воспроизвести вашу проблему на проводнике компилятора Godbolt с помощью AArch64 gcc и ARM gcc. (И я включил пример, который использует __builtin_clz(uiShift) вместо встроенного ассемблера, поэтому он компилируется в clz инструкция по любой архитектуре.)

Кстати, вы могли бы оставить w переопределить размер обоих операндов и просто использовать unsigned int для ввода и вывода. Тогда один и тот же встроенный asm будет работать как с ARM, так и с AArch64. (Но __builtin_clz еще лучше, потому что компилятор понимает, что он делает. например, он знает, что результат находится в диапазоне 0..31, что может позволить некоторые оптимизации.)