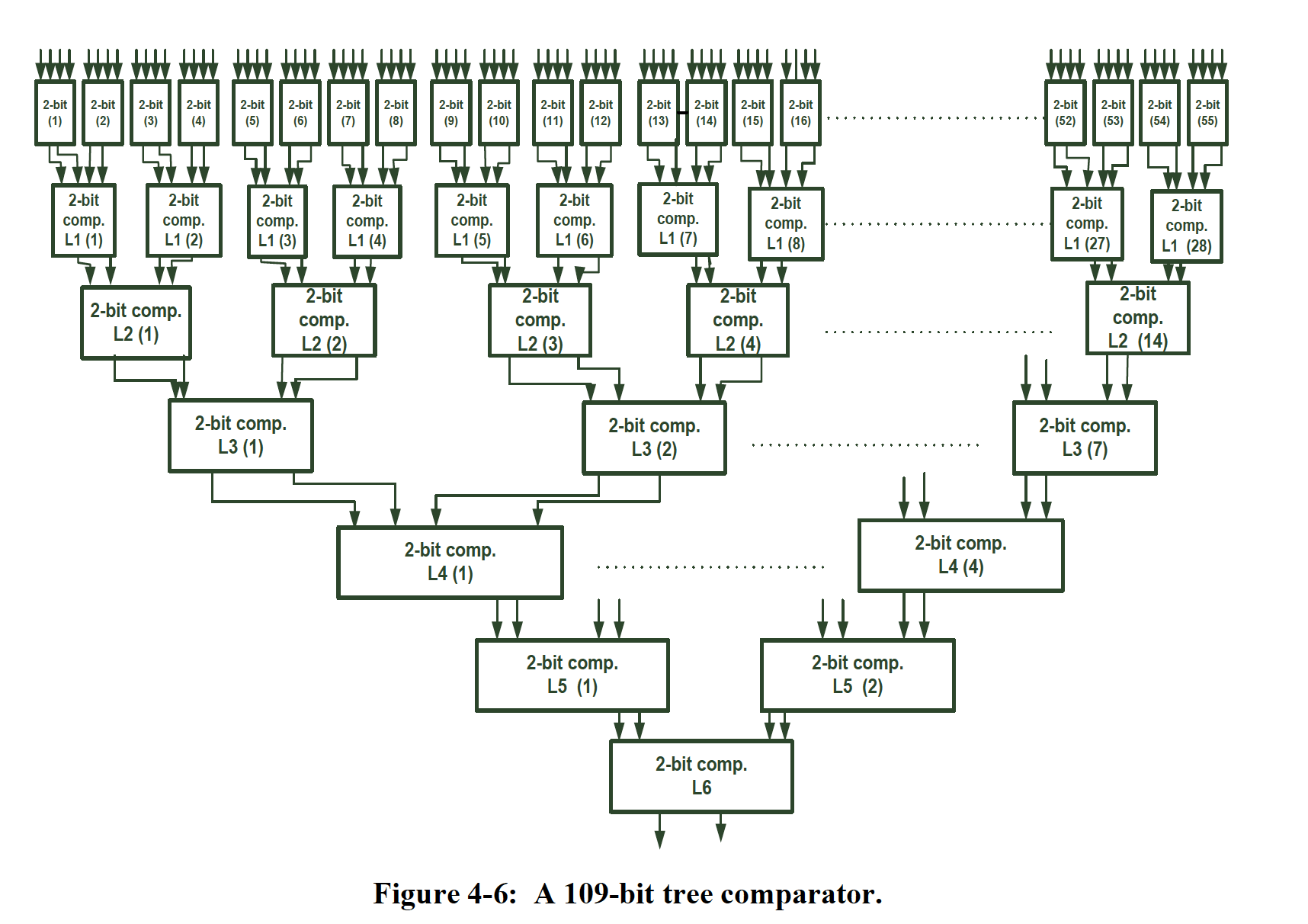

109-битный компаратор дерева с генерацией и для цикла

Я пытаюсь написать код Verilog для 109-битного компаратора дерева, но я все еще новичок в цикле генерации.

Пока я написал некоторый код, но я получаю некоторые ошибки. Кроме того, я не уверен, могу ли я использовать двумерные массивы для сигналов g и l?

parameter NUM_OF_BITS = 109;

parameter NUM_OF_LEVELS = 7;

genvar i;

for (x=0; x<NUM_OF_LEVELS; x=x+1) begin:

generate for (i=0; i<NUM_OF_BITS/((2*x)+1); i=i+1) begin: MCs

mag_comp2_1 mc (in0[2*i+1:2*i],in1[2*i+1:2*i],g[x][i],l[x][i]);

end

endgenerate

NUM_OF_BITS = NUM_OF_BITS/2;

end

3 ответа

Почему бы не определить взаимосвязи для блоков? Таким образом, это будет более удобным для вас.

Неполный пример:

parameter NUM_OF_BITS = 220;

parameter NUM_OF_LEVELS = 7;

genvar i,x;

generate for (x=1; x<NUM_OF_LEVELS; x=x+1)

begin: Ls

wire [NUM_OF_BITS/(2**x)-1:0] output1;

wire [NUM_OF_BITS/(2**x)-1:0] output2;

for (i=0; i<NUM_OF_BITS/(2**x); i=i+1)

begin: MCs

if (x == 1)

begin

// for the first level connect inputs to the module

mag_comp2_1 mc (input1[2*i+1:2*i],input2[2*i+1:2*i],output1[i],output2[i]);

end

else

begin

// for other levels connect ouputs of the previous level

mag_comp2_1 mc (Ls[x-1].output1[2*i+1:2*i],Ls[x-1].output2]2[2*i+1:2*i],output1[i],output2[i]);

end

end

end

endgenerate

parameter NUM_OF_BITS = 220;

parameter NUM_OF_LEVELS = 7;

genvar x,i;

wire [NUM_OF_LEVELS:0][NUM_OF_BITS:0] g, l;

assign g[0] = in0;

assign l[0] = in1;

generate for (x=1; x<NUM_OF_LEVELS; x=x+1) begin: Ls

for (i=0; i<NUM_OF_BITS/(2**x); i=i+1) begin: MCs

mag_comp2_1 mc (g[x-1][2*i+1:2*i],l[x-1][2*i+1:2*i],g[x][i],l[x][i]);

end

end

endgenerate

assign gt = g[NUM_OF_LEVELS][0];

assign lt = l[NUM_OF_LEVELS][0];

Вам нужно что-то вроде следующего. generate.. endgenerate скажите компилятору развернуть все циклы и условные выражения между ключевыми словами. Таким образом, вы получите много экземпляров модуля mag_comp2_1

parameter NUM_OF_BITS = 109;

parameter NUM_OF_LEVELS = 7;

genvar i, x;

generate

for (x=0; x<NUM_OF_LEVELS; x=x+1) begin: externloop

for (i=0; i<NUM_OF_BITS/((2*x)+1); i=i+1) begin: MCs

mag_comp2_1 mc (in0[2*i+1:2*i],in1[2*i+1:2*i],g[x][i],l[x][i]);

end

//NUM_OF_BITS = NUM_OF_BITS/2;

end

endgenerate