Каковы требования для использования операций `shfl` на AMD GPU с использованием HIP C++?

Существует AMD HIP C++, которая очень похожа на CUDA C++. Также AMD создала Hipify для преобразования CUDA C++ в HIP C++ (Portable C++ Code), который может выполняться как на GPU nVidia, так и на GPU AMD: https://github.com/GPUOpen-ProfessionalCompute-Tools/HIP

- Есть требования к использованию

shflоперации на GPU nVidia: https://github.com/GPUOpen-ProfessionalCompute-Tools/HIP/tree/master/samples/2_Cookbook/4_shfl

требование для nvidia

пожалуйста, убедитесь, что у вас есть устройство с поддержкой вычислений версии 3.0 или выше, чтобы использовать операции warp shfl и добавить -gencode arch=compute=30, code=sm_30 nvcc флаг в Makefile при использовании этого приложения.

- Также отметил, что HIP поддерживает

shflдля 64 волнового размера (размер WARP) в AMD: https://github.com/GPUOpen-ProfessionalCompute-Tools/HIP/blob/master/docs/markdown/hip_faq.md#why-use-hip-rather-than-supporting-cuda-directly

Кроме того, HIP определяет переносимые механизмы для запроса архитектурных функций и поддерживает больший 64-битный размер волны, который расширяет тип возвращаемого значения для функций между рядами, таких как голосование и перемешивание, с 32-битных до 64-битных.

Но какой из графических процессоров AMD поддерживает функции shfl или какая-либо поддержка AMD GPU shfl потому что на AMD GPU это реализовано с использованием Local-памяти без аппаратных инструкций от регистра к регистру?

Для GPU nVidia требуется 3,0 или выше (CUDA CC), но каковы требования для использования shfl операции на AMD GPU с использованием HIP C++?

1 ответ

Да, в GPU GCN3 есть новые инструкции, такие как

ds_bpermuteа такжеds_permuteкоторый может обеспечить функциональность, такую как__shfl()и даже большеЭти

ds_bpermuteа такжеds_permuteинструкции используют только маршрут локальной памяти (LDS 8,6 ТБ / с), но фактически не используют локальную память, это позволяет ускорить обмен данными между потоками: 8,6 ТБ / с <скорость <51,6 ТБ / с: http: // gpuopen.com / драмы-GCN-сборка кросс-пер-операция /

Они используют оборудование LDS для маршрутизации данных между 64 полосами волнового фронта, но на самом деле они не записывают в местоположение LDS.

- Также есть Data-Parallel Primitives (DPP) - это особенно полезно, когда вы можете использовать его, поскольку операционная система может читать регистры соседних рабочих элементов напрямую. Т.е. DPP может получить доступ к соседнему потоку (рабочему элементу) на полной скорости ~51,6 ТБ / с

http://gpuopen.com/amd-gcn-assembly-cross-lane-operations/

теперь большинство векторных инструкций может выполнять межканальное чтение с полной пропускной способностью.

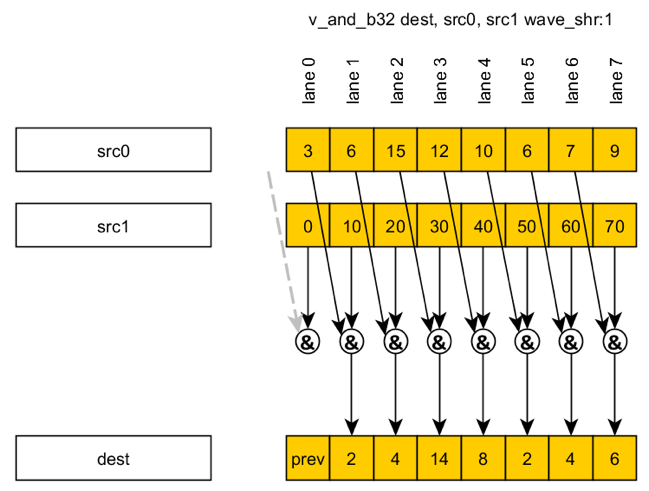

Например, wave_shr-инструкция (сдвиг волнового фронта вправо) для алгоритма сканирования:

Подробнее о GCN3: https://github.com/olvaffe/gpu-docs/raw/master/amd-open-gpu-docs/AMD_GCN3_Instruction_Set_Architecture.pdf

Новые инструкции

- "SDWA" - адресация вспомогательных слов обеспечивает доступ к байтам и словам VGPR в инструкциях VALU.

- "DPP" - параллельная обработка данных позволяет командам VALU получать доступ к данным из соседних линий.

- DS_PERMUTE_RTN_B32, DS_BPERMPUTE_RTN_B32.

...

DS_PERMUTE_B32 Перестановка вперед. Не пишет никакой памяти LDS.